# **Control Methods for Multilevel Converters**

Hamza Ahmed M. Makhamreh

Submitted to the Institute of Graduate Studies and Research in partial fulfillment of the requirements for the degree of

> Doctor of Philosophy in Electrical and Electronic Engineering

Eastern Mediterranean University February 2019 Gazimağusa, North Cyprus Approval of the Institute of Graduate Studies and Research

Assoc. Prof. Dr. Ali Hakan Ulusoy Acting Director

I certify that this thesis satisfies the requirements as a thesis for the degree of Doctor of Philosophy in Electrical and Electronic Engineering.

Prof. Dr. Hasan Demirel Chair, Department of Physics

We certify that we have read this thesis and that in our opinion, it is fully adequate, in scope and quality, as a thesis of the degree of Doctor of Philosophy in Electrical and Electronic Engineering.

> Prof. Dr. Osman Kükrer Supervisor

> > **Examining Committee**

1. Prof. Dr. Ahmet Hava

2. Prof. Dr. İbrahim Sefa

3. Prof. Dr. Hasan Kömürcügil

4. Prof. Dr. Hüseyin Özkaramanlı

5. Prof. Dr. Osman Kükrer

## ABSTRACT

This thesis aims to develop new control methodologies for the Packed U-Cell (PUC) converter. The main problem lies in the structure of the PUC converter, where it is a hybrid type of multilevel converter (MLC) similar to cascaded H-bridge converters. From the control prospective, the topology has discrete digital control inputs, thus conventional modulation techniques cannot be directly applied to the converter. Proper control methods have to be introduced in order to make use of the great advantages of the PUC converter. These control methods have to be simple in implementation for industrial environment with low switching frequency. Additionally, the newly proposed control methods should have advantages over the existing ones.

In the first attempt of this thesis, a modified version of model predictive control (MPC) has been integrated to control grid connected PUC inverters. Mainly, the cost function is formulated to guarantee the stability of the controlled system. Then, the gains associated with the controlled variables are eliminated in order to simplify the control. The proposed controller has shown great features in terms of stability and low average switching frequency.

In the second attempt of this thesis, the interesting features of sliding mode theory are utilized to serve the control problem in a better way. The proposed controller is very simple to implement with low computation time, which reduces the computational burden on the controller. The controller aims to allocate the control input which stabilizes both the grid current and the auxiliary capacitor voltage in the grid connected PUC inverter.

Lastly, the control problem of the PUC rectifier with a dual output is targeted using Lyapunov-based MPC. This attempt is done in order to prove the workability of the controller for three control variables. In this method Lyapunov-based MPC doesn't require gain tuning as in the PUC inverter problem. Load current measurements are eliminated by making use of the mathematical model of the PUC converter. This significantly reduces the cost and simplifies the control algorithm, where no current sensors are used for the load measurements.

For all proposed methods, simulations and experimental tests were done in order to justify the correctness of the proposed methods. Dynamic tests and parameter mismatch tests are carried out to measure the controller response and to show the robustness feature of the proposed controllers.

**Keywords:** Finite control set, Lyapunov control, model predictive control, multilevel converter, packed U-Cell converter, sliding mode control.

ÖZ

Bu tezin amacı PUC cevirgecler için yeni denetleme yöntemleri geliştirmektir. Bu çevirgeçlerde esas sorun, ardarda bağlanmış H-köprüye benzer çoklu-seviyeli melez bir sınıf olmalarından kaynaklanan yapılarından dolayıdır. Denetleme açısından bakıldığında, bu çevirgeçlerin topolojisinde ayrık ve sayısal denetleme girişleri vardır. Dolayısıyla, geleneksel kipleme yöntemleri bu çevirgeçlere doğrudan uygulanamaz. PUC çevirgeçlerinin avantajlarından faydalanan uygun denetleme yöntemlerinin Bu yöntemlerin, endüstriyel ortamlara uygun ve düşük geliştirilmesi gerekir. anahtarlama sıklıklarına sahip basit bir şekilde gerçekleştirilebilmeleri gerekir. Buna ek olarak, önerilen denetleme yöntemlerinin var olanlara göre avantajlarının olması Model öngörücü denetlemenin (MÖD) çoklu-seviyeli çevirgeçler gibi gerekir. endüstriyel uygulamalarda kullanılması da dikkate alınarak, bu yöntemin farklılaştırılmış bir türü şebekeye bağlı PUC evirgeçlerinin denetlenmesi için Esas olarak eder işlevi, denetlenen sistemin kararlılığını garanti geliştirilmiştir. edecek şekilde düzenlenmiştir. Denetlenen değişkenlere ait kazançlar, bazı varsayımlar kullanılarak ve denetlemeyi basitleştirmek amacı ile elenmiştir. Onerilen denetleyicinin, kararlılık ve düşük ortalama anahtarlama sıklığı gibi önemli özelliklere sahip olduğu gözlenmiştir.

Bu tezdeki ikinci girişimde, denetleme sorununa daha iyi çözümler getirmek için, kayan kiplemeli denetleme kuramının önemli özelliklerinden yararlanılmıştır. Önerilen denetleyici, denetleyicinin üzerindeki hesaplama yükünü azaltan, oldukça basit bir tarzda gerçekleştirilebilmektedir. Denetleyicinin amacı denetleme girişlerini, şebekeye bağlı PUC evirgeçinin şebekeye verdiği akımı ve sığaç gerilimini kararlı duruma getirecek şekilde belirlemektir.

Son olarak, çift çıkışlı PUC doğrultucuların denetleme sorununu Lyapunov tabanlı MÖD kullanarak çözmek hedeflendi. Bu girişim, üç değişkenli denetleme durumunda denetleyicinin çalışabilir olduğunu göstermek için yapıldı. Önerilen yöntemde, PUC evirgeçinde olduğu gibi, Lyapunov tabanlı MÖD kazanç ayarına gereksinim duymamaktadır. PUC çevirgeçinin matematiksel modeli kullanılarak yük akımı ölçümleri elenmiştir. Bu da, denetleme algoritmasını basitleştirmiş ve akım duyaçlarına gereksinimi ortadan kaldırarak ederi önemli ölçüde azaltmıştır.

Önerilen ve PUC topolojisine uygulanan denetleme yönteminin başarımını göstermek amacıyla benzetim ve deney sonuçları sunulmuştur. Denetleyicinin yanıt hızını ölçmek ve sağlamlık özelliğin göstermek amacı ile dinamik ve parametre uyuşmazlığı sınamaları yapılmıştır.

Anahtar Kelimeler: Sınırlı denetim kümesi, model öngörülü denetim, çok katmanlı çevirgeç, istiflenmiş U-hücre çevirgeç, kayan kipli denetim.

# DEDICATION

Dedicated to my family.

## ACKNOWLEDGMENT

My deepest gratitude goes to my supervisor Prof. Dr. Osman Kükrer for his constant support and wholehearted collaboration in my thesis. The list of skills I have learned from him is too long to be included here. Therefore, simply thanks for everything, for being a great teacher, for great research support, advice and for correcting this thesis. Thanks for guiding me through this time, it has been and will be an honor and great pleasure working with you.

I am deeply indebted to the department's chair, Prof. Dr. Hasan Demirel for his unconditioned support. What I appreciated most was the flexibility he gave me and the freedom he has offered me that allowed me to focus on research, and produce quality research outcomes.

My personal appreciation goes to Prof. Dr. Ahmet Hava, Prof. Dr. İbrahim Sefa, Prof. Dr. Hasan Kömürcügil, and Prof. Dr. Hüseyin Özkaramanlı, for accepting to be in my jury. Their valuable comments and suggestions have truly helped me to further improve my thesis writing and contents.

I am most grateful to my parents who were always there to support me and to share my thoughts. I want to thank my mother for her love and endless support, thanks for always being there for me and for being here in Cyprus during my defense. Thanks to all my brothers and sister who always encourage me to finish this long journey. Thanks to my father in law Abu Nedal and my mother in law who took care for Zaid during writing this thesis. The effort you spent during that period is invaluable. Thanks to all his family for their great support.

Yet, in the end, my special thanks go to my life partner and dearest person Maysarah who reminded me that there is a life beyond the school. Without her I would not have made it here. Thanks for understanding that time was often scarce and for always encouraging me. Thanks for listening to me when I needed someone to talk to, thanks for all the nights we spent managing time and scheduling for the next-step goals.

After all, I believe that the research I did during my PhD is just an exercise and the best is coming with time. This is just the beginning.

# TABLE OF CONTENTS

| ABSTRACT iii                                        |

|-----------------------------------------------------|

| ÖZ v                                                |

| DEDICATION vii                                      |

| ACKNOWLEDGMENT viii                                 |

| LIST OF TABLES xiii                                 |

| LIST OF FIGURES xiv                                 |

| LIST OF SYMBOLS AND ABBREVIATIONSxviii              |

| 1 INTRODUCTION                                      |

| 1.1 Introduction1                                   |

| 1.2 Thesis Objectives                               |

| 1.3 Literature Survey   3                           |

| 1.4 Contribution of the Thesis                      |

| 1.5 Conclusion                                      |

| 2 PACKED U-CELL TOPOLOGY                            |

| 2.1 The Need for MLC                                |

| 2.2 Flying Capacitor Converter (FCC) 10             |

| 2.3 Cascaded H-bridges Converter 11                 |

| 2.4 Packed U-cell Topology 12                       |

| 2.5 The PUC7 Inverter 14                            |

| 3 LYAPUNOV-BASED MODEL PREDICTIVE CONTROL OF A PUC7 |

| GRID-CONNECTED MULTILEVEL INVERTER 18               |

| 3.1 Introduction                                    |

| 3.2 Lyapunov-Based Controller Design                |

| 3.2.1 Theory Overview                                                                                                                  | 18                                          |

|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| 3.2.2 Error Function Evaluation                                                                                                        | 19                                          |

| 3.3 Lyapunov-Based MPC Design                                                                                                          | 20                                          |

| 3.3.1 System States Prediction                                                                                                         | 21                                          |

| 3.3.2 Lyapunov Cost Function and The Control Algorithm                                                                                 | 22                                          |

| 3.3.3 Stability Analysis                                                                                                               | 23                                          |

| 3.4 Robustness Analysis                                                                                                                | 27                                          |

| 3.5 Comparison with classical MPC                                                                                                      | 29                                          |

| 3.6 Simulation and Experimental Results                                                                                                | 31                                          |

| 3.6.1 Steady State Test                                                                                                                | 32                                          |

| 3.6.2 Parameter Mismatch Test                                                                                                          | 35                                          |

| 3.6.3 Dynamic Response Test                                                                                                            | 35                                          |

| 3.6.4 Active and Reactive Power Flow Tests                                                                                             | 36                                          |

|                                                                                                                                        |                                             |

| 3.7 Conclusions                                                                                                                        | 37                                          |

|                                                                                                                                        | 37<br>A                                     |

| 3.7 Conclusions                                                                                                                        | A                                           |

| 3.7 Conclusions4 AN EFFECTIVE SLIDING MODE CONTROL DESIGN FOR                                                                          | A<br>38                                     |

| 3.7 Conclusions<br>4 AN EFFECTIVE SLIDING MODE CONTROL DESIGN FOR<br>GRID-CONNECTED PUC7 MULTILEVEL INVERTER                           | A<br>38<br>38                               |

| <ul> <li>3.7 Conclusions</li> <li>4 AN EFFECTIVE SLIDING MODE CONTROL DESIGN FOR<br/>GRID-CONNECTED PUC7 MULTILEVEL INVERTER</li></ul> | A<br>38<br>38<br>39                         |

| <ul> <li>3.7 Conclusions</li></ul>                                                                                                     | A<br>38<br>38<br>39<br>39                   |

| <ul> <li>3.7 Conclusions</li></ul>                                                                                                     | A<br>38<br>38<br>39<br>39<br>40             |

| <ul> <li>3.7 Conclusions</li> <li>4 AN EFFECTIVE SLIDING MODE CONTROL DESIGN FOR<br/>GRID-CONNECTED PUC7 MULTILEVEL INVERTER</li></ul> | A<br>38<br>38<br>39<br>39<br>40<br>43       |

| <ul> <li>3.7 Conclusions</li></ul>                                                                                                     | A<br>38<br>38<br>39<br>39<br>40<br>43<br>44 |

| <ul> <li>3.7 Conclusions</li></ul>                                                                                                     | A<br>38<br>39<br>39<br>40<br>43<br>44<br>46 |

| 4.3.2 Parameters Mismatch Test                           | 49 |

|----------------------------------------------------------|----|

| 4.3.3 Voltage ride-through capability test               | 49 |

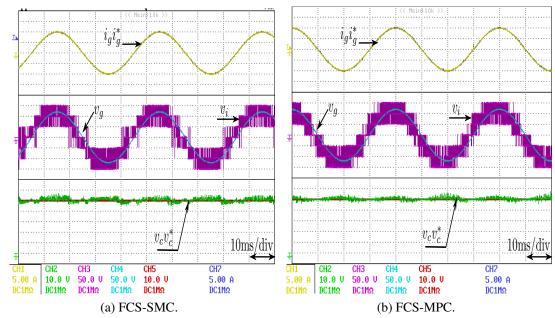

| 4.4 Comparison with Conventional FCS-MPC                 | 50 |

| 4.4.1 Computational Load Comparison                      | 52 |

| 4.4.2 Steady State Performance                           | 53 |

| 4.5 Conclusions                                          | 55 |

| 5 A REDUCED SENSOR LYAPUNOV-BASED MODEL PREDICTIVE CONTR | OL |

| DESIGN FOR A PUC7 DUAL OUTPUT RECTIFIER                  | 56 |

| 5.1 Introduction                                         | 56 |

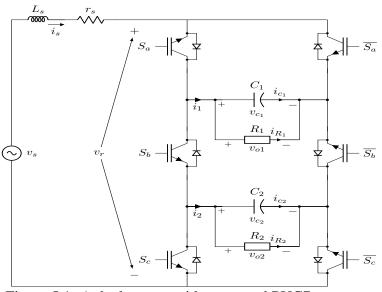

| 5.2 Mathematical Model of the PUC7 Rectifier             | 57 |

| 5.3 Controller Design                                    | 60 |

| 5.3.1 Discrete Model and System States Prediction        | 61 |

| 5.3.2 Cost Function Design                               | 62 |

| 5.3.3 Lyapunov-based MPC Algorithm                       | 64 |

| 5.4 Simulation and Experimental Results                  | 66 |

| 5.4.1 Steady State Test                                  | 68 |

| 5.4.2 Dynamic Performance Test                           | 69 |

| 5.4.3 Parameter Mismatch                                 | 71 |

| 5.5 Conclusions                                          | 72 |

| 6 CONCLUSIONS AND FUTURE WORK                            | 73 |

| 6.1 Coclusions                                           | 73 |

| 6.2 Future Works                                         | 74 |

| REFERENCES                                               | 91 |

# LIST OF TABLES

| Table 2.1: Comparison table: FCC, CHB and PUC topology devices count for seve | n |

|-------------------------------------------------------------------------------|---|

| levels voltage output                                                         | 3 |

| Table 2.2: PUC7 Switching States And Terminal Voltages    1                   | 6 |

| Table 3.1: Simulation and Experimental Parameters    3                        | 0 |

| Table 3.2: Comparison table: Classical MPC vs Proposed Method    3            | 1 |

| Table 4.1: Simulation and Experimental Parameters.    4                       | 9 |

| Table 4.2: Computational load comparison between conventional FCS-MPC vs. th  | e |

| proposed FCS-SMC for one sampling time 5                                      | 1 |

| Table 4.3: Comparison table: SM control algorithm vs Classical MPC.       54  | 4 |

| Table 5.1: PUC7 Switching States And Terminal Voltages                        | 8 |

| Table 5.2: Simulation and Experimental Parameters.    6                       | 6 |

# **LIST OF FIGURES**

| Figure 2.1: Flying capacitor   | rs converter topology generates up to 7 levels output           |

|--------------------------------|-----------------------------------------------------------------|

| waveform                       |                                                                 |

| Figure 2.2: Cascaded H-brid    | lge topology consisting of three cells H-bridges 11             |

| Figure 2.3: Schematic of a 7   | 2-Level Packed U-Cell (7L-PUC) converter 12                     |

| Figure 2.4: Grid-connected     | PUC7 inverter 15                                                |

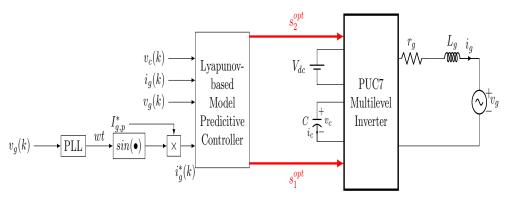

| Figure 3.1: Block diagram o    | f the proposed Lyapunov-based MPC controller 22                 |

| Figure 3.2: Stability region   | comprised of half-planes corresponding to all switching         |

| inputs                         |                                                                 |

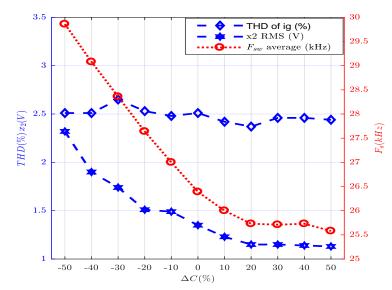

| Figure 3.3: Capacitance value  | ue mismatch versus average switching frequency, grid            |

| current total harmonic distort | tion and capacitor voltage RMS error. $(T_s=25\mu s)$ 28        |

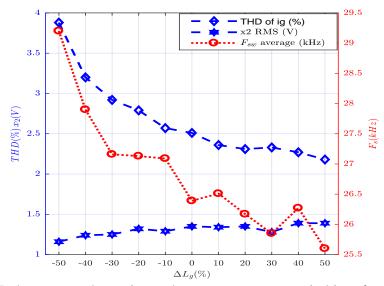

| Figure 3.4: Inductance valu    | e mismatch versus average switching frequency, grid             |

| current total harmonic distort | tion and capacitor voltage RMS error. $(T_s=25\mu s)$ 28        |

| Figure 3.5: Steady state and   | dynamic response comparison of conventional MPC in              |

| [1] and proposed MPC. (top)    | : grid current, grid current reference and the error $x_1$ (A), |

| (bottom): 7-level inverter out | put voltage $v_i$ (V)                                           |

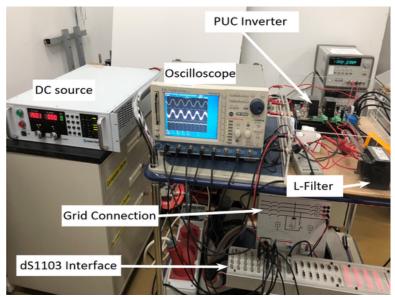

| Figure 3.6: Experimental tes   | st bench for PUC7 grid inverter                                 |

| Figure 3.7: Simulation resul   | ts during a steady state injection of active power into the     |

| grid. (a) Grid voltage (60V/d  | div), grid current and its reference (5A/div), and inverter     |

| output voltage (100V/div).     | (b) Switching control signals of the three pairs of             |

| switches                       |                                                                 |

| Figure 3.8: Simulation and experimental results (corresponds to figure 3.7) of          |

|-----------------------------------------------------------------------------------------|

| capacitor voltage during a steady state injection of active power into the grid (10A    |

| peak current reference)                                                                 |

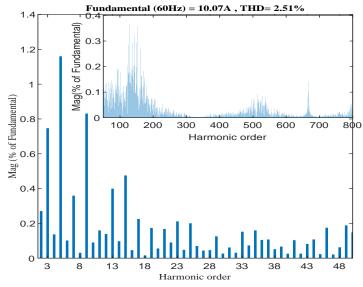

| Figure 3.9: Harmonic spectrum of grid current with respect to the fundamental           |

| component                                                                               |

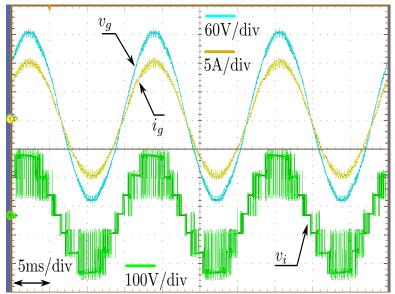

| Figure 3.10: Experimental results during a steady state injection of active power into  |

| the grid                                                                                |

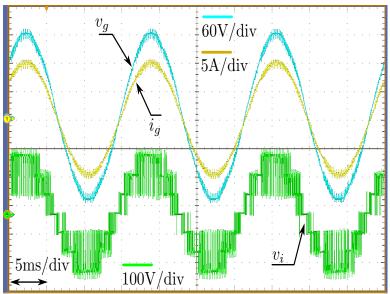

| Figure 3.11: Experimental results during a steady state injection of active power into  |

| the grid, with $+30\%$ mismatch in $L_g$                                                |

| Figure 3.12: Experimental results during a steady state injection of active power into  |

| the grid, with $+30\%$ mismatch in <i>C</i>                                             |

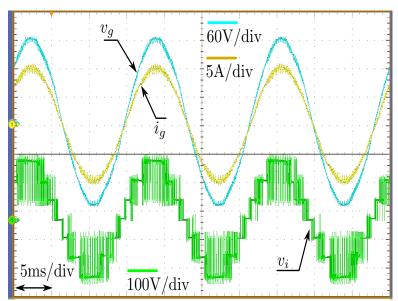

| Figure 3.13: Experimental results during a 100% step change in current reference        |

| within 2 fundamental cycles                                                             |

| Figure 3.14: Experimental results showing inverter and grid voltages, with grid current |

| leading by $20^{\circ}$                                                                 |

| Figure 3.15: Experimental results showing inverter and grid voltages, with grid current |

| lagging by $20^{\circ}$                                                                 |

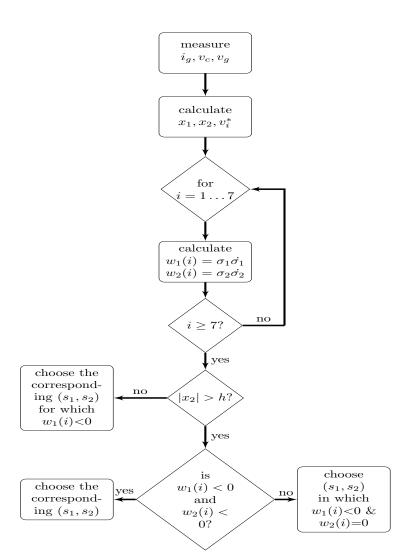

| Figure 4.1: Flowchart of FCS-SMC algorithm                                              |

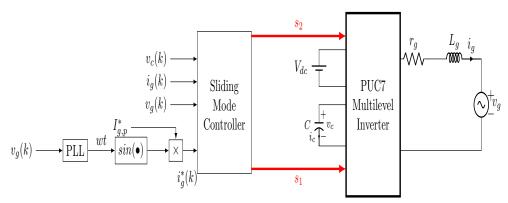

| Figure 4.2: Block diagram of the proposed FCS-SMC controller                            |

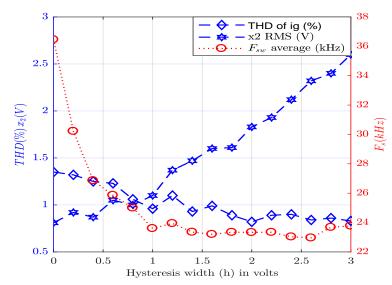

| Figure 4.3: Simulation results of PUC performance using FCS-SMC algorithm with          |

| varying <i>h</i>                                                                        |

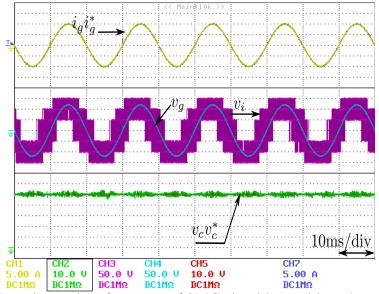

| Figure 4.4: Experimental performance of SMC algorithms without hysteresis               |

| h = 0. 45                                                                               |

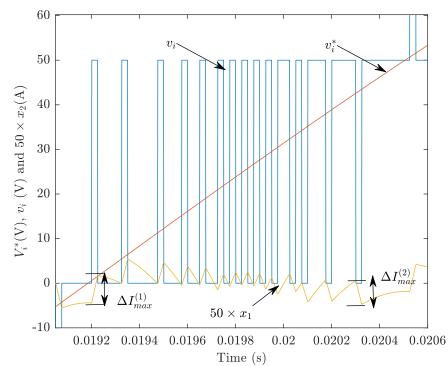

| Figure 4.5:   | Current error ripple, inverter output voltage and inverter voltage reference                           |

|---------------|--------------------------------------------------------------------------------------------------------|

| assuming ca   | apacitor voltage error is zero 46                                                                      |

| Figure 4.6:   | Experimental setup 47                                                                                  |

| Figure 4.7:   | Experimental test under dynamic response test of FCS-SMC algorithm for                                 |

| 100% chang    | ge in the grid reference current                                                                       |

| Figure 4.8:   | Experimental results of FCS-SMC under $-30\%$ mismatch in <i>L</i> 50                                  |

| Figure 4.9:   | Experimental results of FCS-SMC under $+30\%$ mismatch in <i>C</i> 50                                  |

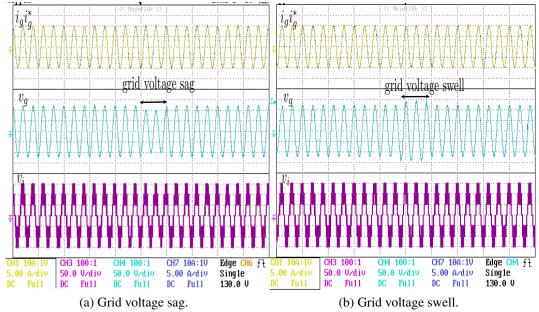

| Figure 4.10   | Experimental voltage ride-through capability of FCS-SMC. (top): grid                                   |

| current, (mi  | ddle): disturbed grid voltage, (bottom): 7-level output voltage 51                                     |

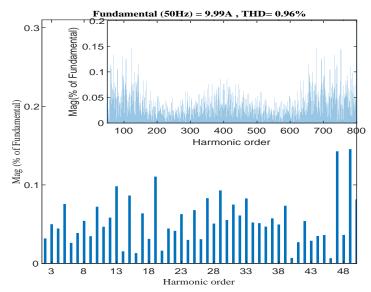

| Figure 4.11   | Harmonic spectrum of grid current with respect to the fundamental                                      |

| component.    |                                                                                                        |

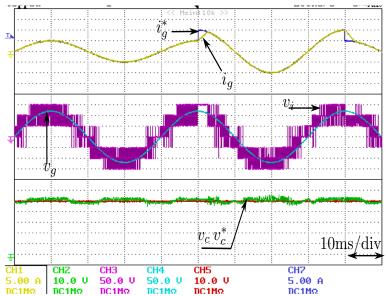

| Figure 4.12   | Experimental results during active power injection to the grid (10A peak)                              |

| at steady sta | ate. (top): grid current and it's reference, (middle): inverter output voltage                         |

| and grid vol  | tage, (bottom): capacitor voltage and it's reference                                                   |

| Figure 5.1:   | A dual output grid-connected PUC7 converter                                                            |

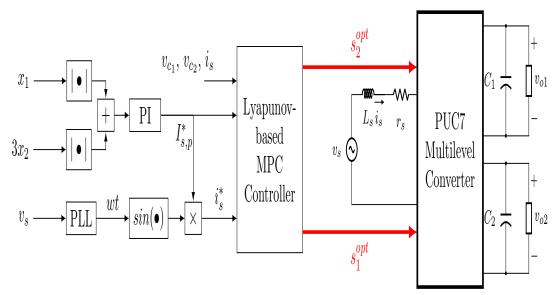

| Figure 5.2:   | Lyapunov-based FCS-MPC block diagram 59                                                                |

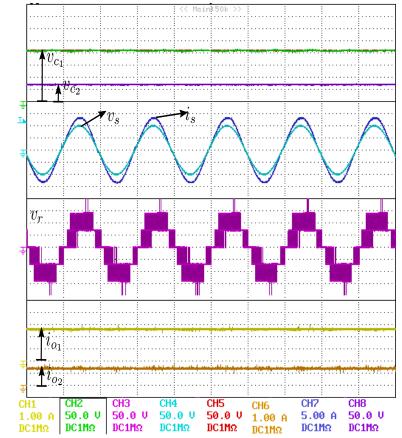

| Figure 5.3:   | Experimental results of PUC7 rectifier performance during steady state.                                |

| The load read | sistors are $R_1 = 80\Omega$ and $R_2 = 50\Omega$                                                      |

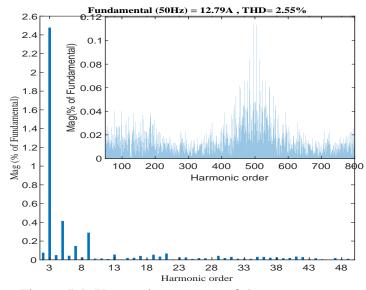

| Figure 5.4:   | Harmonic spectrum of the source current                                                                |

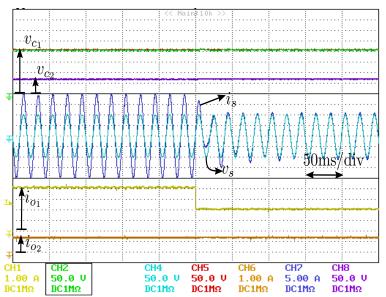

| Figure 5.5:   | Experimental results of PUC7 rectifier performance for step change in the                              |

| first load (R | $R_1$ changed from 100 to 50 $\Omega$ , and $R_2 = 50\Omega$ unchanged)                                |

| Figure 5.6:   | Experimental results of PUC7 rectifier performance for step change in the                              |

| second load   | $(R_2 \text{ changed from } 20 \text{ to } 50 \Omega, \text{ and } R_1 = 50\Omega \text{ unchanged}).$ |

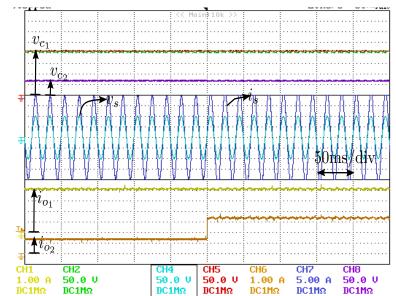

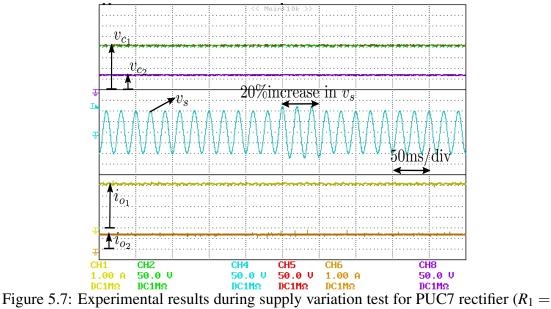

| Figure 5.7:             | Experimental results during supply variation test for PUC7 rectifier ( $R_1$ = | =  |

|-------------------------|--------------------------------------------------------------------------------|----|

| $R_2=50\Omega).$        |                                                                                | 9  |

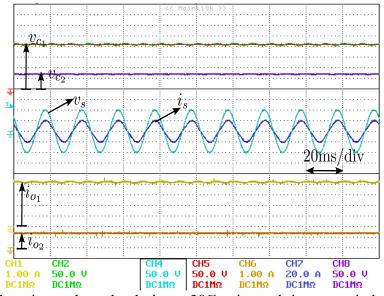

| Figure 5.8:             | Experimental results during +30% mismatch in source inductance value           | ıe |

| $L_s (R_1 = R_2$        | $=50\Omega$ )                                                                  | 0  |

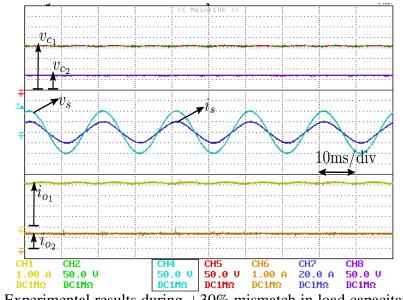

| Figure 5.9:             | Experimental results during +30% mismatch in load capacitances value           | 2S |

| $C_1$ and $C_2$ ( $R_1$ | $R_1 = R_2 = 50\Omega$ )                                                       | 1  |

# LIST OF SYMBOLS AND ABBREVIATIONS

| CHB     | Cascaded H-Bridge                           |

|---------|---------------------------------------------|

| FCC     | Flying Capacitors Converters                |

| FCS-MPC | Finite Control Set Model Predictive Control |

| FCS-SMC | Finite Control Set Sliding Mode Control     |

| MLC     | Multilevel Converter                        |

| MLI     | Multilevel Inverter                         |

| MPC     | Model Predictive Control                    |

| NPC     | Neutral Point Clamped                       |

| PI      | Proportional Integral                       |

| PLL     | Phase-Locked-Loop                           |

| PUC     | Packed U-Cell                               |

| PUC5    | 5-Level Packed U-Cell                       |

| PUC7    | 7-Level Packed U-Cell                       |

| SM      | Sliding Mode                                |

| SMC     | Sliding Mode Controller                     |

| THD     | Total Harmonic Distortion                   |

# **Chapter 1**

# **INTRODUCTION**

## **1.1 Introduction**

With the rapid proliferation of renewable energy systems, the need for efficient and high-performance power conversion capabilities has become vital. A Multilevel Converter (MLC) is one among many recent technologies to address this issue. Nowadays, MLC has become a mature technology which is thriving hastily with the growth of renewable energy usage. The limited voltage blocking capability of the power switches is the major reason behind the development of multilevel converters. Though this capability has been improved with the improvement of production technologies, the reachable voltage is still lower than the service voltage of high voltage equipment. Moreover, multilevel converters are key factors in improving the power quality in power conversion systems [2].

Researchers in the field of industrial power electronics are making considerable efforts to improve energy efficiency, power density, reliability, and reduce overall cost of MLCs. The advantage behind using MLCs includes the possibility to use low voltage-rated switches, achieving low-distortion output current waveform, reducing the switching events as well as the size of output filters. The structure of MLCs allows their employment with renewable energy sources and battery systems. The redundant states in MLCs, which may occur naturally, make it possible to achieve fault tolerant operation [3, 4].

#### **1.2 Thesis Objectives**

As the packed U-Cell (PUC) converter is introduced as a high density power solution in industrial applications, this indeed has side effects on the performance of the converter. Indeed, specially designed controllers are required for this compact form of converter. In this section, the main objectives of the thesis are listed to overcome the difficulties in the controller design of the PUC. Firstly, when the PUC is introduced for grid connected inverter applications, we have two main concerns regarding controller design: 1) gain tuning; 2) simplicity of design. These concerns lead to think of a new design procedure in order to achieve the required goals. Thus, Lyapunov-based model predictive control is presented in Chapter 3 as a solution to overcome the existing problems in conventional model predictive controller.

Furthermore, it is crucial to have a computationally simple and easy-to-implement algorithm which doesn't require excessive processing time and memory. Additionally we need to further reduce the switching frequency of the PUC inverter. This is possible by introducing an allowable error in the auxiliary capacitor voltage to the benefit of reducing the average switching frequency. These objective were attainable as presented in Chapter 4. The solution derived based on sliding mode theory, where each of the error variable was designed into a separate sliding function.

Lastly, Lyapunov-based model predictive control is applied to the PUC7 rectifier. The main objectives (in addition to the advantages gained from the Lyapunov-based model predictive control) is to reduce the number of sensors used in the real implementation. This was possible by estimating the load currents from the mathematical model of the converter. The control problem solution is presented in Chapter 5.

## **1.3 Literature Survey**

Classical MLCs in both literature and industry include: Neutral Point Clamped (NPC) [5–8], Flying Capacitor (FCC) [9–11], and Cascaded H-Bridge (CHB) [12–14] Converters. Recently, there have been a lot of interesting research on multilevel converters using nonlinear control methods [15–19], while other research use predictive control and also model predictive control [20–22].

The PUC topology is a MLC, which was originally proposed by Ounejjar et al. [23–27]. Besides its simple construction, the PUC converter has the advantage of reduced number of switches and DC sources as compared to other classical MLC topologies. Moreover, the reduced number of switches implies a reduced number of redundant states, which adds challenges to the control design [1, 23, 25, 26, 28–35]. The PUC topology has been tested in several applications such as three-phase active filters [36], static VAR compensators [37, 38], dynamic voltage restorers [39] and other industrial applications [40–47].

In [29], authors have proposed a novel six band hysteresis controller for the converter operating in inverter and rectifier mode. In rectifier mode for instance, the error of the two output load voltages are regulated by means of a PI controller, then by using a hysteresis controller the rectifier line current is controlled. It was clearly shown that the controller has fast dynamic, strong robust behavior and simplicity in implementation, but it still suffers from variable switching frequency. On the other hand, a fixed switching frequency could be maintained when PID controllers are used, with the integration of the PWM technique, as reported in [26, 28]. In [46] capacitor voltage balancing was possible by means of choosing a proper firing angle of the switches, which was extensively addressed in [48] for generalized multilevel

inverters.

Model predictive control (MPC) is used in plants which have complex dynamics and can flexibly handle non-linearities as well as constraints on variables. In such plants, the dynamic model of the controlled plant is used to produce the optimal control input at the current time instant [49]. The "optimal" choice is determined by solving an optimization problem according to some error cost function, which is evaluated based on the measured states, the previous states and the predicted ones. The predicted states require estimation which is obtained based on the mathematical model of the plant, and the control action is taken over one finite horizon (longer horizons are also possible). The control input may be continuous in time, taking values in a certain range, or it may consist of a finite set of discrete inputs.

The nature of the control input emerges from the controlled system's structure. Therefore MPC when applied to finite control set problems has a variable switching frequency output and the optimization problem is solved by evaluating an online cost function for all the possible control inputs. In continuous input MPC problems, the controller requires a modulator, resulting in fixed switching frequency and the optimization problem may be solved offline. For both types of MPC problems, constraints may be included in the controller in order to further improve the performance of the controlled system [50]. This feature is considered as another great advantage of model predictive-based controllers especially when the model includes nonlinearities [51].

With the existing fast digital controllers, MPC offers intuitive solutions for powerelectronics-related control problems along with a remarkable ease of implementation, efficient and satisfactory performance [32, 52, 53]. MPC can solve multi-objective control problems such as the control of the PUC inverter [1,39,54,55]. By using MPC, an optimal sequence of the control signals is obtained over the prediction horizon by the minimization of a multi-objective cost function (simultaneous control of the grid current and the capacitor voltage). Then, the first switching pattern of the control sequence is conveyed to the inverter switches and the entire "prediction-optimization" operation is repeated at each sampling period [1,56]. For inverter applications, in [54] the cost function was defined in terms of the load current as well as capacitor voltage errors, coupled with weighting factors to be selected such that minimum total harmonic distortion (THD) of the grid current, and low capacitor voltage error are obtained.

However, the main drawbacks of the MPC techniques are the involvement of considerable time intervals between the control actions (computation time) to allow the minimization of the cost function, complex tuning of the control gains (weighting factors), and high switching frequency [57–61]. Thus, sliding mode control may offer a simple and effective alternative for the PUC control problem. Sliding mode control is a particularly interesting technique [62–68] where the principle consists in bringing, regardless of the initial conditions, the representative point of the system behavior along a cross-surface (sliding surface) by the application of switching elements in the control law. In addition, the set-valued control ensures that the system representative state reaches the sliding surface in a finite time and the system starts moving toward the steady state. The sliding surface is designed as a linear combination of the system states, which usually represent system errors. The control technique then becomes insensitive to disturbances and parametric variations, which makes it a good candidate for the PUC converter under study.

## **1.4 Contribution of the Thesis**

The main contribution of this thesis is the ability to soften the existing nonlinear control methods in order to overcome the difficulties in the PUC converter. The well-known Lyapunov control theory is adapted to serve the existing model predictive control method in order to overcome the structure of the PUC topology and to improve the performance of the model predictive controller. The reported Lyapunov based predictive control is a novel method which will solve the existing limitations in the model predictive control, such as gain tuning, inclusion of additional constraints and simplicity in implementation. On the other hand, the existing sliding mode control theory is set in a simple form which yielded a great reduction in the processing time and further simplicity in the implementation. The reported sliding mode control is model independent type of control, where the control algorithm has the merit of reducing the average switching frequency at the expense of allowable error in the capacitor voltage. Additionally, the presented control methods are not restricted to this topology but can be directly applied to other topologies as well. In this thesis each chapter is dedicated to a novel control technique applied to multilevel Packed U-Cell converters.

In Chapter 3 a new Lyapunov-based model predictive controller is proposed for a 7-Level Packed U-Cell (PUC7) grid-connected inverter. The cost function of the proposed model predictive controller is designed from a system stability point of view, inspired by Lyapunov control theory. The proposed controller eliminates the need for gains that are used to penalize errors on controlled system variables associated with cost function coefficients, as seen in classical MPC-based controllers. Therefore, the control design problem is significantly simplified. In addition, the average switching frequency is also reduced, as shown in both simulation and experimental results, leading to a reduction in switching losses. Simulation and experimental tests on a PUC7 lab prototype, demonstrate the excellent performance of the proposed control system, in terms of high disturbance rejection, robustness to parameter mismatches, and fast dynamic response. Such features qualify the proposed control strategy as a good candidate for grid-tied applications.

Chapter 4 proposes an effective sliding mode controller (SMC) for a grid-connected PUC7 inverter. The aim is to design a simple controller that deals effectively with the complex control problem of the PUC7 inverter (multi-objective control problem). The selection of the control actions is achieved according to the system state error at every sampling time regardless of the previous values, which makes the control technique model- independent. The control algorithm evaluates online two cost functions (one for each state error) which are derived based on sliding mode (SM) theory, and selects the optimal control input in order to satisfy the reaching conditions of the two cost functions. Compared to the existing solutions, the proposed SMC technique ensures lower average switching frequency by tuning the hysteresis bandwidth of the capacitor voltage error. The fast implementation, needless of gain tuning, and simple design procedure are the main features of the proposed algorithm. Simulation and experimental results are presented to prove the effectiveness of the proposed technique in controlling the PUC7 inverter with high dynamic performance and robustness against disturbances and parameters mismatch.

Chapter 5 proposes a Lyapunov-based model predictive controller design for dual output multilevel PUC7 rectifier. The proposed controller is seen as an improvement of the conventional model predictive controller, where the cost function is derived from a stability point-of-view. The controller selects the control input which corresponds to the minimum value of the Lyapunov cost function. Though the cost function includes three state variables' errors (two capacitor voltages and source current errors), the proposed controller is characterized by its easy implementation, no gain tuning requirement as for conventional MPC, and less sensors demand (the controller predicts the loads measurement based on the mathematical model of the PUC rectifier).

#### **1.5 Conclusion**

It is evident that the development of the multilevel converter is ongoing and a rapidly growing technology with applications in the electrical power industry. As the need increases for high density power converters, topology designers are looking for more compact form of the device, which leads to topological complexity of the power converter. The compact form reduces the number of passive elements used and semiconductor devices; yet it complicates the control design procedure. This thesis presents competitive solutions to the existing ones in the field of control of PUC power converters. The solutions presented here are aimed to be simple, effective and are based on a mathematical foundation where further studies can be conducted on them. Furthermore, the presented control methods can be easily applied to other types of converters such as cascaded h-bridge and flying capacitors.

# **Chapter 2**

# PACKED U-CELL TOPOLOGY

#### 2.1 The Need for MLC

During the last decades, many multilevel topologies were discussed in the literature, which have found their way to industrial applications [69, 70]. There are numerous review and tutorial papers which classify and summarize recent developments in topologies and control methods of MLCs [3, 71–74]. In 1981, Nabae has invented a new type of multilevel converter known as the neutral point clamped (NPC) inverter [75]. In 1992, Meynard et. al. developed the flying capacitor (FCC) type of multilevel converter [76]. After a few years, F. Peng et al. developed the cascaded H-bridge multilevel converter (CHB) for static var generation, which is used for different applications afterwards [77]. The aforementioned three types of converters are known as traditional multilevel converters which have limitations when the number of output voltage levels is increased.

The need for multilevel converters is due the following reasons:

- 1. In order to reduce the harmonic contents in the output waveform and to reduce the voltage stress across the semiconductor switches.

- 2. The ability to generate high voltages by employing lower rated devices which have limited blocking capabilities.

- 3. To reduce the switching frequency (i.e. switching losses).

#### 4. To reduce the filter size and the overall cost.

In the following, the flying-capacitor converter, the cascaded H-bridge converter and then the Packed U-cell topology are presented. A comparison between the PUC and the traditional types of multilevel converter is given.

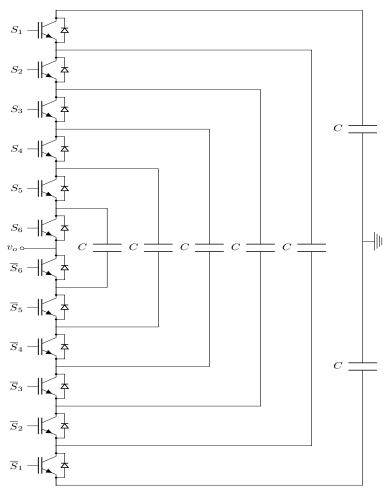

Figure 2.1: Flying capacitors converter topology generates up to 7 levels output waveform.

## **2.2 Flying Capacitor Converter (FCC)**

The word "flying" is used because the capacitor's voltage is floating with respect to the ground and the capacitors are used to "clamp" the voltage to higher/lower levels than the dc source(s) [78–80]. Theoretically, FCC can produce an infinite number of output voltage levels but most of the applications were limited to 5, 7 and 9 level output due to the complexity in the control, gate driver design and capacitor voltage balancing

issues [81, 82]. Figure. 2.1 shows a seven level FCC; the capacitor closer to the dc voltage source has higher voltage stress, while the outermost capacitors have lower voltage stresses and lower switching frequency, as well.

FCC consists of multiple cells nested in each other where each cell has a single capacitor and two power switches. A converter having N cells uses N capacitors and 2N switches to produce N+1 different output voltage levels including the zero output level.

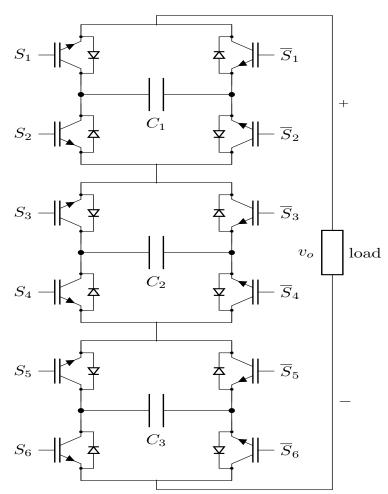

Figure 2.2: Cascaded H-bridge topology consisting of three cells H-bridges.

# 2.3 Cascaded H-bridges Converter

Figure 2.2 shows the configuration of a 7-level output CHB converter. The converter consists of three H-bridge cells connected in series in order to produce a higher output

voltage. Though the structure makes packing and building such a converter easy, yet this converter requires isolated dc sources, and the capacitor voltages need a special balancing control technique [83–86]. The input dc sources may be equal or may vary according to the application requirements. The CHB is a modular converter, but it needs separate dc supplies that could be provided from a multi-winding phase-shifted transformer, which reduces the power density and increases the system cost. A CHB having N cells can produce 2N+1 output voltage levels including the zero level by utilizing N capacitors and 4N switches.

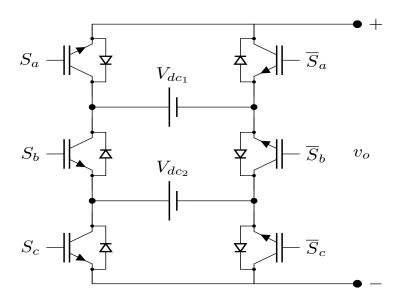

Figure 2.3: Schematic of a 7-Level Packed U-Cell (7L-PUC) converter.

#### 2.4 Packed U-cell Topology

The PUC topology shown in figure 2.3 is considered as a hybrid cascaded H-bridge type of converter. It consist of 6 power switches and two capacitors, resulting in a compact-form MLI structure. One of the capacitors is replaced by a dc source in case of inverter operation mode. The PUC topology introduces a reduction in the number of power switches and the passive elements used in the construction. Table 2.1 shows a comparison between the FCC, CHB and PUC converter topologies in terms of the

number of capacitors and switches for a seven-level output voltage waveform.

Realization of more than five levels in conventional multilevel topologies is a challenging task, due to stability, scalability and modularity limits. However, PUC converter can produce 5- and 7- level output voltages if the second capacitor voltage is controller to half and one-third of the first capacitor dc source, respectively. A higher number of voltage levels implies a small filter size and further reduction in the total harmonic distortion (THD) of the current output in inverter operation mode (or smaller THD of the grid current in rectifier operation mode).

Table 2.1: Comparison table: FCC, CHB and PUC topology devices count for seven levels voltage output.

| No. of     | FCC | CHB | PUC |  |

|------------|-----|-----|-----|--|

| Capacitors | 6   | 3   | 2   |  |

| Switches   | 12  | 12  | 6   |  |

The recently proposed PUC technology brought enormous improvements to MLC technology as compared to the classical MLCs, such as:

- Reduction in the number of passive elements used in the topology.

- Reduction in the number of semiconductor devices, thus reduction in the overall cost.

- Improved AC and DC side power quality without the need for additional bulky harmonic filters.

However, all these benefits brought by the PUC converter are linked to challenges in terms of control complexity; thus PUC has the following disadvantages:

- Bilinear structure, where the control inputs are included in the closed-loop system matrix.

- Control design complexity, where linear and nonlinear control methods cannot be directly applied to the PUC converter.

- Control-associated challenges in terms of modelling and simulations.

Moreover, despite the serious challenges associated with the PUC approach, benefiting from its superior performance and attractive features are worth investing in research work. This will to bring new tools and findings for a better understanding and high performance operation.

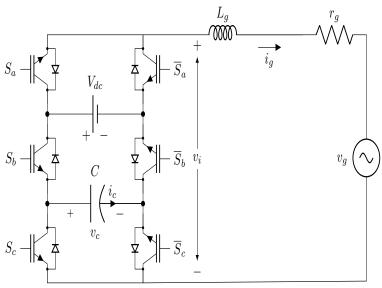

## 2.5 The PUC7 Inverter

A PUC inverter depicted in figure 2.4, has six power switches  $(S_a, \overline{S}_a, S_b, \overline{S}_b, S_c, \overline{S}_c)$ , one DC source, and one auxiliary capacitor, with their voltages denoted as  $V_{dc}$  and  $v_c$ , respectively. Switches are controlled as complementary pairs with their switching states defined as,

$$s_k = \begin{cases} 1 & \text{if } S_k \text{ is closed } (S_k \text{ is open}) \\ \\ 0 & \text{if } S_k \text{ is open } (\overline{S}_k \text{ is closed}) \end{cases}$$

where  $k \in \{a, b, c\}$ .

The PUC single-phase inverter is connected to the utility grid through a line filter with inductance value designated as  $L_g$ , and its parasitic resistance as  $r_g$ . The inverter's control objective is to inject to the grid, at a controlled power factor, a sinusoidal current  $i_g$ , which follows a current reference  $i_g^*$ . This can be accomplished by designing a controller, which selects the proper switching states for the converter so current is injected to the grid at minimum THD, while keeping the capacitor voltage close to its reference value  $v_c^*$ .

The far right column of Table 2.2 refers to the charging state of the capacitor with

Figure 2.4: Grid-connected PUC7 inverter.

respect to the grid current direction and the applied switching state. The symbols used are ( $\uparrow$ : charging), ( $\downarrow$ : discharging), and ( $\backsim$ : no change). The pair of switching functions ( $s_1, s_2$ ) are defined as

$$s_1 = s_a - s_b \tag{2.1}$$

$$s_2 = s_b - s_c$$

Using Table 2.2 and (2.1), the inverter output voltage can be written as,

$$v_i = s_1 V_{dc} + s_2 v_c \tag{2.2}$$

The capacitor dynamics is expressed as,

$$i_c = C \frac{dv_c}{dt} = -s_2 i_g, \tag{2.3}$$

| l | <i>s</i> <sub>1</sub> | <i>s</i> <sub>2</sub> | s <sub>a</sub> | s <sub>b</sub> | s <sub>c</sub> | v <sub>i</sub>  | $v_i\Big _{v_c=E}^{V_{dc}=3E}$ | $i_g > 0$    | <i>ig</i> < 0 |

|---|-----------------------|-----------------------|----------------|----------------|----------------|-----------------|--------------------------------|--------------|---------------|

| 1 | +1                    | 0                     | 1              | 0              | 0              | $V_{dc}$        | 3 <i>E</i>                     | $\sim$       | $\sim$        |

| 2 | +1                    | -1                    | 1              | 0              | 1              | $V_{dc} - v_c$  | 2E                             | $\uparrow$   | $\downarrow$  |

| 3 | 0                     | +1                    | 1              | 1              | 0              | V <sub>c</sub>  | Ε                              | $\downarrow$ | $\uparrow$    |

| 4 | 0                     | 0                     | 1              | 1              | 1              | 0               | 0                              | ~            | $\sim$        |

| 4 | 0                     | 0                     | 0              | 0              | 0              | 0               | 0                              | $\sim$       | $\sim$        |

| 5 | 0                     | -1                    | 0              | 0              | 1              | $-v_c$          | -E                             | $\uparrow$   | $\downarrow$  |

| 6 | -1                    | 1                     | 0              | 1              | 0              | $-V_{dc} + v_c$ | -2E                            | $\downarrow$ | $\uparrow$    |

| 7 | -1                    | 0                     | 0              | 1              | 1              | $-V_{dc}$       | -3E                            | $\sim$       | $\sim$        |

Table 2.2: PUC7 Switching States And Terminal Voltages

while the grid model and the current dynamics can be written as

$$\frac{di_g}{dt} = -\frac{r_g}{L_g}i_g + \frac{1}{L_g}(v_i - v_g).$$

(2.4)

One can define the grid current error as  $x_1 = i_g - i_g^*$ , where  $i_g^*$  represents the grid current reference signal. Similarly, the capacitor voltage error may be defined as  $x_2 = v_c - v_c^*$ , where  $v_c^* = E$  is a constant DC voltage reference for the capacitor. In this seven-level PUC inverter, the DC reference voltage (*E*) is taken to be one-third of the DC supply voltage  $V_{dc} = 3E$ , in order to produce 7-level inverter output voltage. From the above equations the current error derivative can be written as

$$\dot{x}_{1} = \frac{di_{g}}{dt} - \frac{di_{g}^{*}}{dt} = \frac{1}{L_{g}} \left\{ s_{1}V_{dc} + s_{2}v_{c} - \left(v_{g} + r_{g}i_{g} + L_{g}\frac{di_{g}^{*}}{dt}\right) \right\}$$

(2.5)

Using  $i_g = x_1 + i_g^*$ , and  $v_c = x_2 + v_c^*$ , one can obtain,

$$\dot{x}_1 = \frac{1}{L_g} \left\{ s_1 V_{dc} + s_2 \left( x_2 + v_c^* \right) - r_g x_1 - v_i^* \right\}$$

(2.6)

One can define the reference voltage of the grid inverter output  $v_i^*$  as,

$$v_i^* = v_g + r_g i_g^* + L_g \frac{di_g^*}{dt}$$

(2.7)

Similarly, after substituting the expression of  $i_g = x_1 + i_g^*$  in (2.3), the capacitor voltage error may be written as,

$$\dot{x}_2 = -\frac{1}{C} s_2 \left( x_1 + i_g^* \right) \tag{2.8}$$

In the next Chapter, derivation of the inverter control law is mathematically developed and thoroughly discussed.

# **Chapter 3**

# LYAPUNOV-BASED MODEL PREDICTIVE CONTROL OF A PUC7 GRID-CONNECTED MULTILEVEL INVERTER

## **3.1 Introduction**

In this chapter a model-based predictive control method with a cost function derived intuitively from Lyapunov's control theory is presented. Furthermore, the selection process of cost function gains is omitted in the proposed method. Thus the proposed cost function eliminates the need for optimization and tuning of the weighting factors associated with the states error. Due to the usage of a Lyapunov-based cost function, stability of the controlled system is guaranteed. A robustness study is presented, simulations and experimental results show the effectiveness of the proposed control scheme, which achieves a fast dynamic response, robust performance, and low-THD grid current.

#### **3.2 Lyapunov-Based Controller Design**

#### 3.2.1 Theory Overview

Mathematical model of the PUC grid connected inverter is given in Section 2.5. Lyapunov direct method of stability is a tool to study the stability of the controlled system by examining the variation of an "energy-like" scalar function, called Lyapunov function  $V(\mathbf{x})$ . This method has shown its effectiveness in the applications

of power electronics, where disturbances and robustness are the main keys to ensure power quality to the controlled system [87]. The Lyapunov function can be defined in terms of system state errors, represented by the vector  $\mathbf{x}$ . Assume that the equilibrium of controlled system is at the origin  $\mathbf{x} = \mathbf{0}$ . When the energy function becomes zero, the system is settled at the equilibrium point, and if the energy function is rapidly increasing, then the system is unstable, and is asymptotically stable if energy is decreasing. The stability of a system is guaranteed if the following conditions hold [88]:

- 1)  $V(\mathbf{x})$  is positive definite.

- 2)  $\dot{V}(\mathbf{x})$  is negative definite.

- 3)  $V(\mathbf{x})$  goes to  $\infty$  as  $\|\mathbf{x}\| \to \infty$ .

Geometrically, condition 1) implies that the Lyapunov function is a bowl-like function upward, with minimum at the equilibrium point. Condition 2) implies that the rate of energy change will drive the state towards the equilibrium point. The last condition assures that error state is located on a closed contour around the equilibrium point.

#### **3.2.2 Error Function Evaluation**

The design goal is to simultaneously control the injected grid current as well as the capacitor voltage. In order to achieve this goal, a Lyapunov function in terms of system's errors is suggested as the following,

$$V(\mathbf{x}) = \frac{1}{2}\alpha_1 x_1^2 + \frac{1}{2}\alpha_2 x_2^2$$

(3.1)

where  $\alpha_1$  and  $\alpha_2$  are real positive numbers, which must be properly selected. It is clear that the above function is positive definite. Lyapunov control theory states that, stability of the controlled system presented by (2.3) and (2.4) is guaranteed if we insure that for all values of **x**,

$$\dot{V}(\mathbf{x}) < 0 \tag{3.2}$$

Derivative of (3.1) with respect to time yields,

$$\dot{V}(\mathbf{x}) = \alpha_1 x_1 \dot{x}_1 + \alpha_2 x_2 \dot{x}_2.$$

(3.3)

Using equations (2.6) and (2.8) in (3.3) one can get,

$$\dot{V}(\mathbf{x}) = \frac{1}{L_g} s_2 x_1 x_2 \left( \alpha_1 - \frac{L_g}{C} \alpha_2 \right) - \frac{\alpha_2}{C} x_2 s_2 i_g^* + \frac{\alpha_1}{L_g} x_1 \left( s_1 V_{dc} + s_2 v_c^* - r_g x_1 - v_i^* \right).$$

(3.4)

In order to eliminate the  $x_1x_2$ -term in (3.4), gains are chosen to satisfy  $\alpha_1 = \frac{L_g}{C}\alpha_2$ . Accordingly, (3.4) reduces to,

$$\dot{V}(\mathbf{x}) = \frac{\alpha_1}{L_g} \{ x_1 \left( s_1 V_{dc} + s_2 v_c^* - r_g x_1 - v_i^* \right) - x_2 s_2 i_g^* \}.$$

(3.5)

Equation (3.5) is used to select the control switches pair  $(s_1, s_2)$  such that the derivative of the cost function is generally negative.

## **3.3 Lyapunov-Based MPC Design**

In this section, a model-based predictive controller is derived in discrete-time, based on the derivative of the Lyapunov function in (3.5). Note that (3.5) gives the Lyapunov function derivative in continuous time, with piece-wise constant switching function pair  $(s_1, s_2)$ . Therefore, in order to derive the switching functions that will be applied in the interval  $(kT_s, (k+1)T_s)$ , such that the derivative is negative at the end of this interval, prediction of the derivative at  $(k + 1)T_s$  is required. A Phase-Locked-Loop (PLL) is used to track and extract grid voltage information. Then a grid current reference signal is created with an appropriate phase shift with respect to the grid voltage. Usually, a high level controller generates the grid current reference, given the active and reactive powers to be injected into the grid. Moreover, system states  $(v_c, i_g)$  and grid voltage  $v_g$  are all measured at instant (k). Next, prediction of the states at (k+1) is made, and the state errors at time instant (k+1) are calculated. The switching pair is chosen to minimize the derivative of the Lyapunov function given in (3.5). In the following sections, these calculations are described in detail.

#### 3.3.1 System States Prediction

Using the first order forward Euler approximation, capacitor voltage and grid current in (2.3) and (2.4) are written in discrete form as follows,

$$v_{c}(k+1) = v_{c}(k) - \frac{T_{s}}{C}i_{g}(k)s_{2}(k)$$

$$i_{g}(k+1) = \lambda i_{g}(k) + \frac{T_{s}}{L_{g}}\Big(v_{i}(k) - v_{g}(k)\Big),$$

(3.6)

where  $\lambda = (1 - r_g T_s/L_g)$ . Equation (3.6) is used to predict the states at (k + 1) using variable values at time (k). In addition, one needs to extrapolate the reference current value at (k+1). The first order linear interpolation by means of averaging the previous values is used, as follows,

$$v_g(k+1) = \frac{3}{2}v_g(k) - \frac{1}{2}v_g(k-1)$$

$$i_g^*(k+1) = \frac{3}{2}i_g^*(k) - \frac{1}{2}i_g^*(k-1).$$

(3.7)

Furthermore the inverter reference voltage at (k+1) is predicted as,

$$v_i^*(k+1) = v_g(k+1) + r_g i_g^*(k+1) + \frac{L_g}{T_s} \{ i_g^*(k+1) - i_g^*(k) \}.$$

(3.8)

Making use of (3.6) and the definition of the errors, the grid current error at the time

instant(k+1) is given by

$$x_{1}(k+1) = i_{g}(k+1) - i_{g}^{*}(k+1)$$

$$= \frac{T_{s}}{L_{g}} \left( \frac{L_{g}}{T_{s}} \lambda x_{1}(k) + s_{1}(k) V_{dc} + s_{2}(k) \left[ x_{2}(k) + v_{c}^{*} \right] \right)$$

$$+ Q(k), \qquad (3.9)$$

The term Q(k) is independent from the states and the control input, and given as

$$Q(k) = \lambda i_g^*(k) - \frac{T_s}{L_g} v_g(k) - i_g^*(k+1).$$

(3.10)

Similarly, the capacitor voltage error at (k+1) can be found as

$$x_{2}(k+1) = v_{c}(k+1) - v_{c}^{*}$$

$$= x_{2}(k) - \frac{T_{s}}{C} x_{1}(k) s_{2}(k) - \frac{T_{s}}{C} i_{g}^{*}(k) s_{2}(k).$$

(3.11)

Figure 3.1: Block diagram of the proposed Lyapunov-based MPC controller.

# 3.3.2 Lyapunov Cost Function and The Control Algorithm

From now on, the derivative of Lyapunov function will be referred to as the cost function. The cost function used in this algorithm is evaluated for the next sampling instant (k+1) based on (3.5). The predicted variables from (3.7) - (3.11) are used to determine the errors of the state variables at (k+1). The control block diagram is shown in figure 3.1. After measuring the states of the controlled system, and

Algorithm 1 Lyapunov-based MPC algorithm for PUC7 grid-connected inverter

1: Measure  $v_g(k), i_g(k), v_c(k)$

- 2: Calculate (3.7) and (3.8).

- 3: for l = 1...7 do

5:

- 4: Calculate (3.9) and (3.11).

- Evaluate (3.12).

- ▷ calculating the errors at (k+1) time instant. ▷ evaluating the cost function.

$\triangleright$  prediction of  $v_g, i_g$  and  $v_i^*$

- 6: **return** minimum  $\dot{V}_{\mathbf{x}}(k+1)$

- 7: Choose the switching pair for which  $\dot{V}_x(k+1)$  is minimum

predicting the state values at instance ((k + 1)), errors at time instant (k + 1) are determined. Evaluating equation (3.5) at the time instant (k+1) yields,

$$\dot{V}_{\mathbf{x}}^{(l)}(k+1) = \frac{\alpha_1}{L_g} \Big\{ x_1(k+1) \{ s_1^{(l)}(k) V_{dc} + s_2^{(l)}(k) v_c^* - r_g x_1(k+1) - v_i^*(k+1) \} - x_2(k+1) s_2^{(l)}(k) i_g^*(k+1) \Big\}.$$

(3.12)

where *l* refers to the level index in Table 2.2 in Section 2.5. At time step (k) the control algorithm works as shown in Algorithm 1. It is worth mentioning that the controller targets the minimum of the Lyapunov function  $V(\mathbf{x})$ . Further detailed discussion is entailed in Section 3.3.3. The main advantage of the proposed controller is that there are no gains to be tuned for optimizing the performance. Therefore, a unique performance is expected from this controller. Another main feature is its good robustness against parameter variations, as will be shown in the following sections.

#### **3.3.3 Stability Analysis**

Although predictive control offers superior performance as compared to classical control methods for many power electronics control problems, it still lacks studies on stability and robustness analysis [52, 53]. In this work, the choice of a control strategy based on Lyapunov theory helps to study the stability of the controlled system. In standard Lyapunov theory the stability analysis is done by first finding a positive definite Lyapunov function; then the derivative of this function is proved to be negative definite [88]. This guarantees that the system trajectory is such that the

Lyapunov function decreases, which becomes zero at the equilibrium point. However, the classical approach in Lyapunov stability analysis can't be applied to the problem here because of the followings: 1) the control variables are switching signals, 2) the set of discrete control variables involves a large number of elements ( seven elements). Therefore, the analysis approach we adopted is less rigorous than the common Lyapunov practice. At this step, assume  $r_g = 0$  and substitute (3.9) and (3.11) in (3.12) then one obtains

$$\begin{split} \dot{V}_{\mathbf{x}}(k+1) \\ &= \frac{\alpha_1}{L_g} \left\{ \frac{T_s}{L_g} \left( \frac{L_g}{T_s} \lambda x_1(k) + s_1(k) V_{dc} + s_2(k) \left( x_2(k) + v_c^* \right) \right) \\ &+ Q(k) \right\} \left( s_1(k) V_{dc} + s_2(k) v_c^* - v_i^*(k+1) \right) - \frac{\alpha_1}{L_g} \left\{ x_2(k) - \frac{T_s}{C} x_1(k) s_2(k) - \frac{T_s}{C} i_g^*(k) s_2(k) \right\} i_g^*(k+1) s_2(k) \end{split}$$

(3.13)

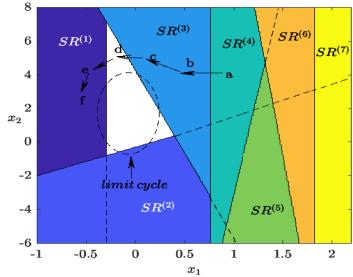

Figure 3.2: Stability region comprised of half-planes corresponding to all switching inputs.

The term  $\alpha_1/L_g$  multiplies both terms in (3.13), so it can be eliminated from the equation because it has no influence on the decision of stability. After eliminating that

term, (3.13) can be written in the following form

$$\dot{V}_{\mathbf{x}}(k+1) = a(k)x_1(k) + b(k)x_2(k) + c(k)$$

(3.14)

where

$$a(k) = \lambda V_{bias} + \frac{T_s}{C} s_2^2(k) i_g^*(k+1)$$

$$b(k) = \frac{T_s}{L_g} s_2(k) V_{bias} - s_2(k) i_g^*(k+1)$$

$$c(k) = \left( Q(k) + \frac{T_s}{L_g} \{ s_1(k) V_{dc} + s_2(k) v_c^* \} \right) V_{bias}$$

$$+ \frac{T_s}{C} s_2^2(k) i_g^*(k) i_g^*(k+1)$$

$$V_{bias} = s_1(k) V_{dc} + s_2(k) v_c^* - v_i^*(k+1)$$

(3.15)

It is clear from (3.14) that the derivative of the Lyapunov function is a time-varying function. In this control problem we have only seven control inputs, each corresponding to an inverter output voltage. The output levels are indicated by the index l = 1...7 as given in Table 2.2. Corresponding to the control inputs, stability regions on the  $x_1x_2$ -plane are defined as

$$SR^{(l)}(k+1) = \{(x_1, x_2) \mid \dot{V}_{\mathbf{x}}^{(l)}(k+1) < 0\}.$$

(3.16)

Note that each of the stability regions is a half-plane on the  $x_1x_2$ -plane. For instance,  $SR^{(1)}(k+1)$  refers to the stability region on the  $x_1x_2$ -plane when the control pair (+1,0) is applied. The inverter output voltage for this case is  $v_i = 3E$  in the steady state. By examining equations (3.8)-(3.11), it is obvious that these functions are time varying functions and they are all involved in calculating (3.12), which is again time varying function. <sup>1</sup>

<sup>&</sup>lt;sup>1</sup>Please refer to the animation files provided with this thesis, which shows the stability regions for one complete cycle.

Refer to figure 3.2, the regions  $SR^{(l)}(k+1)$ , l = 1...7 are shown as the colored halfplanes, where the white region does not belong to any of these regions, hence  $\dot{V}_{\mathbf{x}}(k+1)$ is positive herein. Given a point 'a' on the state plane outside the white region, it can be seen that this point belongs to at least one of the stability regions. In this case the controller chooses the control pair for which  $\dot{V}_{\mathbf{x}}(k+1)$  is minimum (most negative). After control input application the state will be driven in such a direction that the Lyapunov function decreases. This corresponds to the trajectory being directed toward the origin shown as the sequence of points 'a',..., 'f'. Eventually, the trajectory will enter a limit cycle . At this stage, it is important to note that the state errors are in general periodic functions of time (in the steady state). This can be understood by examining equations (3.9) and (3.11). The implication is that the equilibrium of the system is not a single point but a limit cycle.

In case the state enters the white region where  $\dot{V}_{\mathbf{x}}(k+1)$  is positive, the trajectory will be forced to leave this region and enter the limit cycle. It should be noted that in the steady state the average of  $\dot{V}_{\mathbf{x}}(k)$  over one period is zero. A nonzero average value would imply an increasing or decreasing Lyapunov function which is impossible if the system is stable. To maintain zero average for  $\dot{V}_{\mathbf{x}}(k)$  in the steady state, part of the system trajectory should be within the colored regions and the rest in the white region as shown in figure 3.2. Notice that the trajectory will not circle a static region, as shown in the figure, but instead a time-varying region (as shown in the gifs provided with the thesis). An important point to mention here, is that the stability discussions above are valid for any set of system parameters. Using different parameters will only change the regions to a certain degree but the concepts discussed will remain the same.

In order to show the system's stability, it is required to show that the unstable region is

encompassed by many stable regions under all conditions. By doing so, we will ensure that if the state is in the stability region/s the trajectory will be in such a direction as to decrease  $\dot{V}_{\mathbf{x}}(k)$ , and if the state is in the unstable region the state will be directed to the stable region. This is the case even though the stability region is time varying. In conclusion, the system is only stable in the sense of Lyapunov if the unstable region is always closed by different stable regions. The presented analysis, simulation and experimental results show that the stability is verified. Yet, the authors believe that a full mathematical demonstration is still an open topic in a new research work.

# **3.4 Robustness Analysis**

In order to prove robustness of the proposed controller, the system's response has been studied under the effect of capacitor mismatch, as shown in figure 3.3. Simulations are performed for system parameters given in Table 3.1, with the exception that sampling time is chosen as  $T_s = 25 \,\mu s$  at 10A peak reference grid current. The controller employs an estimated value of the capacitance, denoted as  $C_{est}$ , which is different from actual capacitor value, denoted as  $C_{act}$ , where  $\Delta C_2(\%) = \frac{C_{act} - C_{est}}{C_{act}} \times 100$ . As shown in figure 3.3, grid current THD is almost invariant under capacitance mismatch, while capacitor voltage RMS error is slowly increasing as estimated capacitance value increases. The average switching frequency, however, increases up to 17.2 kHz when capacitance mismatch reaches -50%.

Similarly, when a mismatch is applied to the filter inductance value  $L_g$ , the THD of grid current is observed to increase as  $L_{est}$  becomes greater than  $L_{act}$ , as shown in figure 3.4, where  $\Delta L_g(\%) = \frac{L_{act} - L_{est}}{L_{act}} \times 100$ . Also, a similar behavior is noticed for average switching frequency which increases up to 17 kHz for -50% mismatch in  $L_g$ .

Figure 3.3: Capacitance value mismatch versus average switching frequency, grid current total harmonic distortion and capacitor voltage RMS error. ( $T_s=25 \mu s$ ).

From figure 3.4, it can be shown that the distortion of grid current is linked to the mismatch in grid inductance value. On the other hand, a mismatch in the inductance value shows a negligible influence on the capacitor voltage RMS error.

Figure 3.4: Inductance value mismatch versus average switching frequency, grid current total harmonic distortion and capacitor voltage RMS error. ( $T_s=25 \mu s$ ).

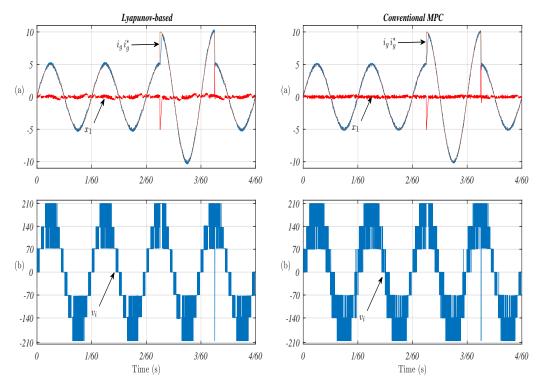

Figure 3.5: Steady state and dynamic response comparison of conventional MPC in [1] and proposed MPC. (top): grid current, grid current reference and the error  $x_1$  (A), (bottom): 7-level inverter output voltage  $v_i$  (V).

# **3.5** Comparison with classical MPC

The proposed controller is compared with another MPC-based method. The authors in [1] have suggested a model based predictive controller with the following normalized cost function,

$$g = \lambda \frac{x_2}{\Delta v_{c,\max}} + \frac{x_1}{\Delta i_{g,\max}}$$

(3.17)

where  $\Delta v_{c,\text{max}} = 2i_g T_s/C$  and  $\Delta i_{g,\text{max}} = 2V_{dc}T_s/L_g$ . The parameter  $\lambda$  is a positive gain associated with the capacitor error, and it should be chosen properly in order to maintain both, low capacitor voltage error and low THD of grid current. The THD of the grid current is defined as

$$THD = \frac{\sqrt{I_2^2 + I_3^2 + I_4^2 + \dots}}{I_1^2}$$

(3.18)

where  $I_n$  is the RMS value of the nth harmonic current, and n=1 is the fundamental component. The RMS value of the capacitor voltage error is defined as

$$x_2$$

(RMS) =  $\sqrt{\frac{1}{T} \int_0^T x_2^2 dt}$  (3.19)

Where *T* is the fundamental period of the grid voltage. Authors in [1] suggest a method to properly choose the gain. The same method is used in this work to obtain the optimal  $\lambda$  value suitable for system used in the experimental setup. Applying method used in [1] yields  $\lambda = 0.149$ , which is used in this comparison test. Figure 3.5 shows steady state and dynamic performance comparison between conventional MPC and the proposed MPC. The steady state performance is shown in the first two cycles and the dynamic performance is shown in the last two cycles due to a step change in current reference.

| Tuble 5.1. Simulation and Experimental Tarameters |            |                     |  |  |

|---------------------------------------------------|------------|---------------------|--|--|

| Parameters                                        | Symbol     | Value               |  |  |

| Dc voltage source                                 | $V_{dc}$   | 210V                |  |  |

| Inverter capacitance                              | С          | 1.5mF               |  |  |

| Grid voltage (RMS) and frequency                  | $V_g, f_g$ | 120V, 60Hz          |  |  |

| Grid inductance and resistance                    | $L_g, r_g$ | $5$ mH, $0.7\Omega$ |  |  |

| Sampling time                                     | $T_s$      | 25µs                |  |  |

Table 3.1: Simulation and Experimental Parameters

The grid current THD and the average switching frequency ( $F_{s,av}$ ) are compared, whereas the capacitor voltage error is kept equal for both methods. The comparison is performed for 10A peak reference current with the system parameter listed in Table 3.1. A summary of the comparative test is listed in Table 3.2.

Although the proposed method has slightly higher THD, as compared to the control

| Parameters       | Classical MPC [1]    | Lyapunov-based MPC |

|------------------|----------------------|--------------------|

| THD of $i_g(\%)$ | 2.10                 | 2.51               |

| $F_{s,av}$ (kHz) | 33.24                | 26.39              |

| $x_2$ RMS (V)    | 1.35                 | 1.36               |

| Gain tuning      | gain is involved     | no gain involved   |

|                  | (tuning is required) | (simple)           |

Table 3.2: Comparison table: Classical MPC vs Proposed Method

method in [1], it has two fundamental advantages, which includes lower switching frequency and ease of implementation. Moreover, in the proposed method, there is no need to tune any gains like  $\lambda$ . In the method proposed in [1],  $\lambda$  needs to be tuned for different grid current references, different sampling time, or new system parameters. On the other hand, in this proposed control method, the derivative function in (3.5) does not involve any tunable parameters.

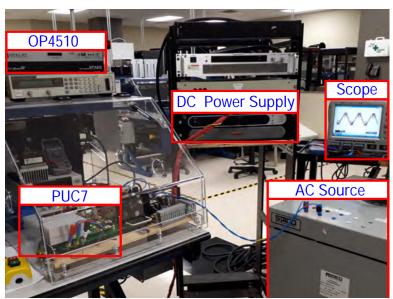

Figure 3.6: Experimental test bench for PUC7 grid inverter.

# 3.6 Simulation and Experimental Results

In order to verify the behavior of the proposed scheme, various simulation scenarios of the 1.5 kVA single-phase grid-connected PUC7 system using SimPowerSystem library from Simulink/MATLAB along with experimental tests have been carried out.

Figure 3.6 shows the test-bench of the experimental setup. The proposed control algorithm is running on the OP4510 real-time controller from OPAL-RT. Specifications and parameters of the controlled system are listed in Table 3.1 for both simulation and experimental tests.

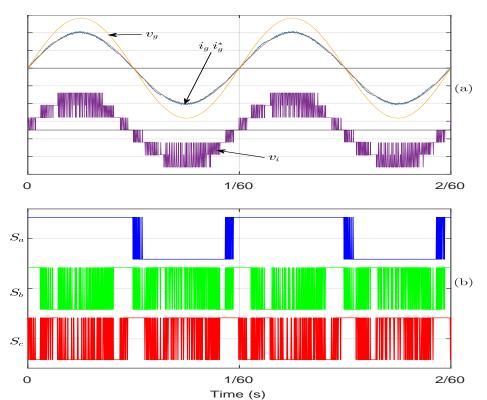

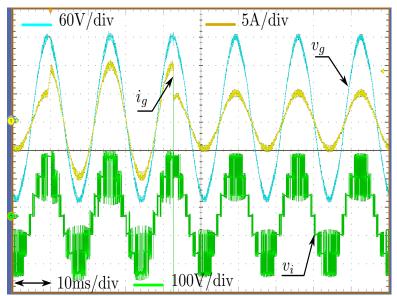

Figure 3.7: Simulation results during a steady state injection of active power into the grid. (a) Grid voltage (60V/div), grid current and its reference (5A/div), and inverter output voltage (100V/div). (b) Switching control signals of the three pairs of switches.

# 3.6.1 Steady State Test

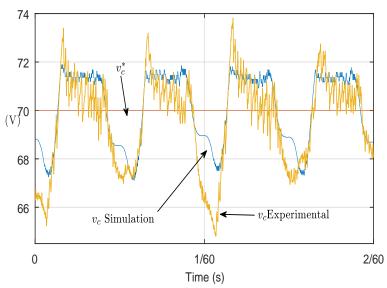

Depicted in figure 3.7 are simulation results showing the low THD of grid current achieved by the proposed control method. Grid current THD is calculated as 2.51% for 10A peak of reference grid current. The capacitor voltage output wave-forms for simulation and experimental tests are given in figure 3.8. The RMS error of the capacitor voltage is 1.36V in the simulation results. Average switching frequency was

Figure 3.8: Simulation and experimental results (corresponds to figure 3.7) of capacitor voltage during a steady state injection of active power into the grid (10A peak current reference).

Figure 3.9: Harmonic spectrum of grid current with respect to the fundamental component.

found to be 26.39 kHz. The average switching frequency is calculated as,

$$F_{s,\mathrm{av}} = \frac{N_{S_a} + N_{S_b} + N_{S_c}}{T_{\mathrm{total}}}$$

(3.20)

where  $N_{S_a}$ ,  $N_{S_b}$ , and  $N_{S_c}$  represent the total number of times the devices switch in a time interval of  $T_{\text{total}}$ , counting turn ON and turn OFF as two separate switching events. For example, when the simulation is run for 10 fundamental periods ( $T_{\text{total}} = 10/60$ ),

Figure 3.10: Experimental results during a steady state injection of active power into the grid.

the devices switch ON and OFF 262, 2104 and 2033 times, respectively.

Figure 3.9 shows the calculated harmonic spectrum of the grid current from simulation results of figure 3.7. Moreover, figure 3.10 shows the experimentally measured voltage and current waveforms of the inverter-grid system at steady-state, with grid current THD measured as 3.57%.

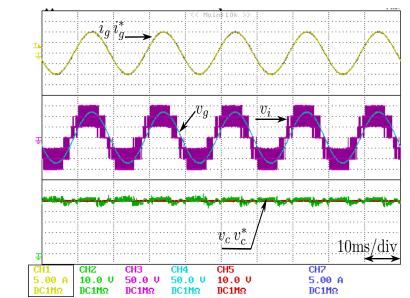

Figure 3.11: Experimental results during a steady state injection of active power into the grid, with +30% mismatch in  $L_g$ .

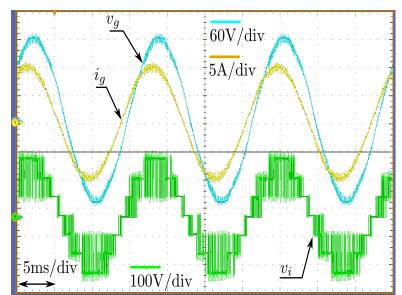

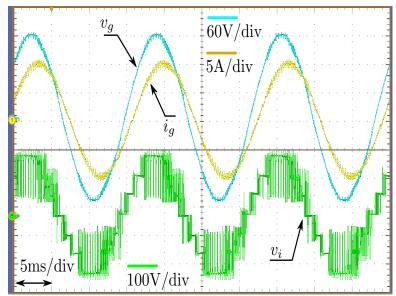

#### 3.6.2 Parameter Mismatch Test

The robustness of the controller is also tested in the experimental system against parameter mismatches. Figure 3.11 shows the measured system waveforms, with a grid current THD measured as low as 3.81%. Similarly, figure 3.12 shows the output waveforms when there is a mismatch in the capacitance value. The output grid current THD is measured as 3.37%. In all the experimental results, it is clear that all 7-Levels of inverter output voltage are well maintained.

Figure 3.12: Experimental results during a steady state injection of active power into the grid, with +30% mismatch in *C*.

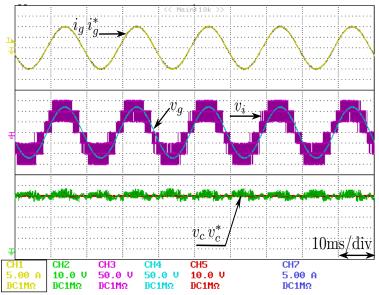

# 3.6.3 Dynamic Response Test

Dynamic response of the controller is measured by applying a step change in the grid current reference amplitude. As can be seen in figure 3.13, the grid current reference amplitude was increased from 5A to 10A peak, corresponding to 100% increase in grid current amplitude, then after 2 fundamental cycles the grid current reference amplitude was reduced back from 10A to 5A. The controller exhibits a fast response

Figure 3.13: Experimental results during a 100% step change in current reference within 2 fundamental cycles.

to the step change in grid current reference, while maintaining a unity power factor power injection to the grid.

Figure 3.14: Experimental results showing inverter and grid voltages, with grid current leading by 20°.

# 3.6.4 Active and Reactive Power Flow Tests