# **Improving Energy Consumption in Networks on Chip using Optimized Algorithms**

Mehdi Taassori

Submitted to the Institute of Graduate Studies and Research in partial fulfillment of the requirements for the degree of

> Doctor of Philosophy in Electrical and Electronic Engineering

Eastern Mediterranean University February 2016 Gazimağusa, North Cyprus Approval of the Institute of Graduate Studies and Research

Prof. Dr. Cem Tanova Acting Director

I certify that this thesis satisfies the requirements as a thesis for the degree of Doctor of Philosophy in Electrical and Electronic Engineering.

Prof. Dr. Hasan Demirel Chair, Department of Electrical and Electronic Engineering

We certify that we have read this thesis and that in our opinion it is fully adequate in scope and quality as a thesis for the degree of Doctor of Philosophy in Electrical and Electronic Engineering.

Prof. Dr. Şener Uysal Supervisor

### ABSTRACT

Network on Chip (NoC) has been suggested as an appropriate and scalable solution for system on chip (SoC) architectures having high communication demands. Power dissipation has become a key factor in the NoCs because of their shrinking sizes. In the first part of the thesis, we propose a new encoding approach aimed at power reduction by decreasing the number of switching activities on the buses. This approach assigns the symbols to data word in such a way that the more frequent words are sent by less power consumption. This algorithm dedicates the symbols with less ones to high probable data and uses transition signaling to transmit data. The proposed method, unlike the existing low power encoding, does not rely on spatial redundancy and keeps the width of the bus constant.

Due to the limitation of the resources in NoC, suitable load distribution over limited resources which is known as mapping optimization problem is a challenging issue. The second part presents an OPtimization technique for Application specifIC NoCs (OPAIC), which aims not only to decrease the energy consumption but also to improve the performance and area of NoCs. Application specific NoCs are preferable since they can be customized to optimize all requirements of the specific applications. OPAIC is composed of two stages to find the optimum NoC; in the first stage, it uses a linearized form of a Quadratic Assignment Problem (QAP) to map tasks on cores to minimize the energy dissipation. In the second stage, due to the colossal effect of router reduction on power consumption of NoC, a Mixed Integer Linear Problem (MILP) is proposed to find the optimum number of the routers for the layout earned in previous stage.

It is also worth mentioning that even though in most of the traditional low power encoding algorithms and optimization techniques the effect of coupling capacitors is ignored, the results show that these capacitors have an increasing contribution in power consumption in the NoCs as the VLSI technology advances and the size of the transistor shrinks. In this dissertation, all evaluation results consider the effect of both self and coupling capacitances in the link power dissipation.

**Keywords:** Network on Chip, low power encoding, switching activity, power consumption, energy dissipation, latency, application specific, optimization, mapping.

Mikro Çip üzerindeki Ağ (MÇüA), Mikro Çip üzerindeki Sistem (MÇüS) mimarileri için yüksek iletişim taleplerine sahip uygun ve ölçeklenebilir bir çözüm olarak önerilmiştir. Küçülen boyutları yüzünden MÇüA'lardaki güç tüketimi oldukça önemli bir faktör haline gelmiştir. Bu tez çalışmasının ilk bölümünde veri yolları üzerindeki anahtarlama sayılarını azaltarak güc tüketiminin düşürülmesini hedefleyen yeni bir şifreleme yaklaşımı önerilmiştir. Bu yaklaşım, daha sık kelimelerin daha düşük güç tüketilerek gönderileceği şekilde sembolleri veri kelimelerine atamaktadır. Bu algoritma daha düşük bir sayılarına sahip sembolleri yüksek olasılıklı verilere tahsis edip veri gönderimi için geçiş sinyalizasyonunu kullanmaktadır. Önerilen yöntem, mevcut olan düşük güçlü şifreleme yönteminin tersine, mekânsal fazlalığa dayanmamakta ve veri yolu genişliğini korumaktadır.

MÇüA kaynaklarındaki sınırlılık dolaysıyla haritalama optimizasyon problemi olarak bilinen sınırlı kaynaklar üzerindeki uygun yük dağılımı tartışma konusu olmuştur. İkinci bölüm, yalnızca güç tüketiminin düşürülmesini hedef almayıp aynı zamanda MÇüA'ların performansı ve alanını da geliştirmeyi amaçlayan Uygulamaya Özel MÇüA'lar için Optimizasyon Tekniği'ni (UÖMOP) sunmaktadır. Belirli uygulamaların tüm gereksinimlerini iyileştirmek üzere özelleştirilebilme özellikleri Uygulamaya özel MÇüA'ları tercih edilebilir kılmıştır. UÖMOP, ideal MÇüA'yı bulmak için iki aşamadan oluşmuştur. Birinci aşamada, enerji tüketiminin en aza indirgenmesi amacıyla çekirdekler üzerinde görevleri planlamak üzere Kareli Atama Problemi'nin (KAP) lineerleştirilmiş bir şekli kullanılmaktadır. İkinci aşamada ise yönlendirici indirgemesinin MÇüA'nin güç tüketimi üzerindeki muazzam etkisi nedeniyle bir önceki aşamada elde edilen düzen için ideal yönlendirici sayısının bulunması amacıyla bir Karışık Tamsayı Lineer Problemi (KTLP) önerilmiştir.

Geleneksel düşük güçlü şifreleme algoritmaları ve optimizasyon tekniklerinin çoğunda bağlantı kapasitörlerinin etkisi dikkate alınmasa bile sonuçların Çok Büyük Boyutlu Entegrasyon (ÇBBE) Teknolojisinin ilerlemesi ile birlikte bu kapasitörlerin MÇüA'lardaki güç tüketimi konusunda artan bir katkıya sahip olduklarını gösterdiği bahsetmeye değer bulunmaktadır.

Anahtar Kelimeler: Mikro Çip üzerindeki Ağ, düşük güçlü şifreleme, anahtarlama işlemı, güç tüketimi, enerji israfı, gecikme, uygulamaya özel, optimizasyon, haritalama.

Dedicated To My Dear Parents

# TABLE OF CONTENTS

| ABSTRACT                                                        | iii |

|-----------------------------------------------------------------|-----|

| ÖZ                                                              | v   |

| DEDICATION                                                      | vii |

| LIST OF TABLES                                                  | xi  |

| LIST OF FIGURES                                                 | xiv |

| LIST OF SYMBOLS/ABBREVIATIONS                                   | xvi |

| 1 INTRODUCTION                                                  | 1   |

| 1.1 Introduction                                                | 1   |

| 1.2 Network on Chip Architecture                                | 2   |

| 1.3 Motivation                                                  |     |

| 1.4 Thesis Overview                                             | 4   |

| 2 LOW POWER ENCODING FOR ON CHIP NETWORKS                       | 6   |

| 2.1 Introduction                                                | 6   |

| 2.2 Literature Review                                           | 7   |

| 2.3 Proposed Method                                             | 9   |

| 2.3.1 MFLP Encoding Approach                                    | 9   |

| 2.3.2 Optimality of MFLP                                        | 15  |

| 2.4 Effective Criteria in the Efficiency of the Proposed Method | 16  |

| 2.5 Evaluation                                                  |     |

| 2.5.1 Evaluation of the Proposed Algorithm                      |     |

| 2.5.1.1 On the Bus                                              |     |

| 2.5.1.2 In the Network on Chip (NoC)                            |     |

| 2.5.1.3 Experimental Results                                    |     |

|                                                                 |     |

|    | 2.5.2 Evaluation of Sensitivity to Network Parameters   | 30          |

|----|---------------------------------------------------------|-------------|

|    | 2.5.2.1 Topology                                        | 30          |

|    | 2.5.2.2 Routing Algorithm                               | 33          |

|    | 2.5.2.3 Number of Nodes                                 | 37          |

|    | 2.5.2.4 Size of the Packet Length                       | 41          |

|    | 2.5.2.5 Number of Virtual Channels                      | 45          |

|    | 2.5.2.6 Link Length                                     | 49          |

|    | 2.6 Overhead                                            | 50          |

|    | 2.7 Summary                                             | 51          |

| 3  | OPTIMIZATION TECHNIQUE TO IMPROVE ENERGY CONSUMPT       | ION         |

| Al | ND PERFORMANCE IN APPLICATION SPECIFIC NETWORKS ON CHIP | <b>'</b> 52 |

|    | 3.1 Introduction                                        | 52          |

|    | 3.2 Literature Review                                   | 54          |

|    | 3.3 Motivation                                          | 57          |

|    | 3.3.1 Power Consumption                                 | 58          |

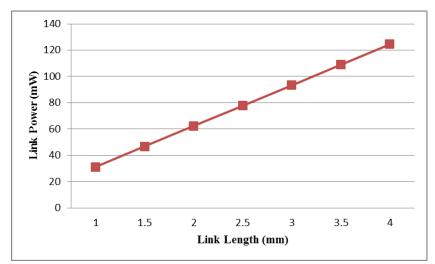

|    | 3.3.1.1 Link Length                                     | 58          |

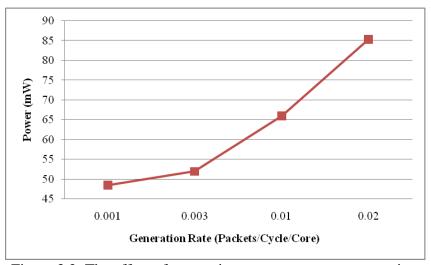

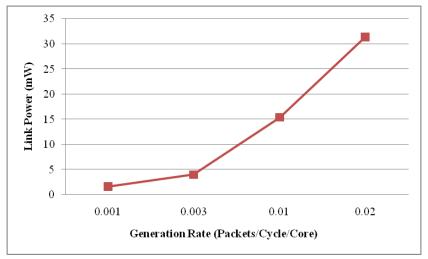

|    | 3.3.1.2 Generation Rate                                 | 59          |

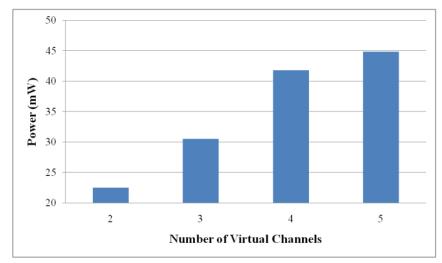

|    | 3.3.1.3 Number of Virtual Channels                      | 60          |

|    | 3.3.2 Latency                                           | 62          |

|    | 3.3.2.1 Generation Rate                                 | 62          |

|    | 3.3.2.2 Number of Virtual Channels                      | 63          |

|    | 3.3.2.3 Generation Rate and Number of Virtual Channels  | 66          |

|    | 3.4 Mathematical Modeling                               | 69          |

|    | 3.4.1 Task to Core Mapping                              | 69          |

|    | 3.4.2 Optimizing of the Number of Routers in NoCs       | 75          |

| 3.5 Experimental Results                                   | 78  |

|------------------------------------------------------------|-----|

| 3.5.1 Benchmarks                                           | 78  |

| 3.5.2 Experimental Results for Mapping Step                | 79  |

| 3.5.3 Experimental Results for the Least Number of Routers | 82  |

| 3.5.4 Experimental Results of Implementation               | 84  |

| 3.6 Summary                                                | 87  |

| 4 CONCLUSION AND FUTURE WORK                               | 89  |

| 4.1 Conclusion                                             | 89  |

| 4.2 Future Work                                            | 90  |

| 4.2.1 Meta-heuristic Algorithms                            | 90  |

| 4.2.2 Fuzzy-based Meta-heuristic Algorithm                 | 93  |

| 4.2.3 Bi-objective Fuzzy-based Meta-heuristic Algorithm    | 96  |

| REFERENCES                                                 | 98  |

| APPENDIX                                                   | 109 |

| Appendix A: List of Journal Publications                   | 110 |

## LIST OF TABLES

| Table 2.1. The code word with different coding                                     |

|------------------------------------------------------------------------------------|

| Table 2.2. Number of Self and Coupling capacitances for different type of          |

| switching activities                                                               |

| Table 2.3. The bit average and energy consumption with various division factors in |

| serial bus                                                                         |

| Table 2.4. The number of switching activities on the parallel bus                  |

| Table 2.5. The link and total power consumption on the parallel bus    27          |

| Table 2.6. The number of switching activities in the NoC    28                     |

| Table 2.7. Comparison of power consumption between MFLP and without coding. 29     |

| Table 2.8. Power consumption for different coding approach in the NoC              |

| Table 2.9. The number of switching activities with different topologies.    31     |

| Table 2.10. The link power consumption with different topologies    31             |

| Table 2.11. The total power consumption with different topologies    32            |

| Table 2.12. Comparison of power consumption between Mesh and Torus                 |

| Table 2.13. The number of switching activities with XY routing algorithm           |

| Table 2.14. The number of switching activities with XY routing algorithm           |

| Table 2.15. The number of switching activities with Duato routing algorithm        |

| Table 2.16. The link and total power consumption with Duato routing algorithm 36   |

| Table 2.17. The number of switching activities with OE routing algorithm           |

| Table 2.18. The link and total power consumption with OE routing algorithm 37      |

| Table 2.19. Comparison of power consumption between XY, Duato and OE 37            |

| Table 2.20. The number of switching activities with 2*2 network                    |

| Table 2.21. The link and total power consumption with 4 nodes    38                |

| Table 2.22. The number of switching activities with 4*4 network               |

|-------------------------------------------------------------------------------|

| Table 2.23. The link and total power consumption with 16 nodes                |

| Table 2.24. The number of switching activities with 8*8 network               |

| Table 2.25. The link and total power consumption with 64 nodes                |

| Table 2.26. Comparison of power consumption between 2*2, 4*4 and 8*8          |

| Table 2.27. The number of switching activities with packet length of 16       |

| Table 2.28. The link and total power consumption with packet length of 16     |

| Table 2.29. The number of switching activities with packet length of 32       |

| Table 2.30. The link and total power consumption with packet length of 32     |

| Table 2.31. The number of switching activities with packet length of 64       |

| Table 2.32. The link and total power consumption with packet length of 64     |

| Table 2.33. Comparison of power consumption between different sizes of packet |

|                                                                               |

| length                                                                        |

| length                                                                        |

|                                                                               |

| Table 2.34. The number of switching activities with 1 virtual channel         |

| Table 2.34. The number of switching activities with 1 virtual channel         |

| Table 2.34. The number of switching activities with 1 virtual channel         |

| Table 2.34. The number of switching activities with 1 virtual channel         |

| Table 2.34. The number of switching activities with 1 virtual channel         |

| Table 2.34. The number of switching activities with 1 virtual channel         |

| Table 2.34. The number of switching activities with 1 virtual channel         |

| Table 2.34. The number of switching activities with 1 virtual channel         |

| Table 2.34. The number of switching activities with 1 virtual channel         |

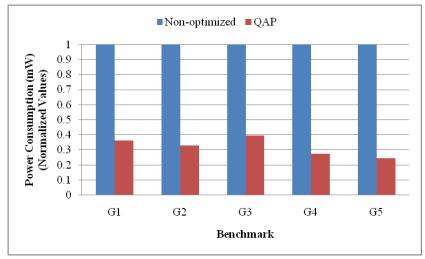

| Table 3.4. | Comparison of | energy consum | nption between | n non-optimized | d and QAP | . 85 |

|------------|---------------|---------------|----------------|-----------------|-----------|------|

| Table 3.5. | Comparison of | OPAIC         |                |                 |           | . 87 |

## LIST OF FIGURES

| Figure 1.1. An NoC example (4x4)                                                         |

|------------------------------------------------------------------------------------------|

| Figure 2.1. Pseudocode of the proposed algorithm                                         |

| Figure 2.2. Root and its children                                                        |

| Figure 2.3. Generation of symbols                                                        |

| Figure 2.4. Comparison of energy consumption with various division factors on the        |

| serial bus                                                                               |

| Figure 2.5. The impact of link length on efficiency of MFLP                              |

| Figure 3.1. The effect of link length on link power consumption                          |

| Figure 3.2. The effect of generation rate on power consumption                           |

| Figure 3.3. The effect of generation rate on link power consumption                      |

| Figure 3.4. The effect of variety of number of virtual channels versus power             |

| consumption in X-Y routing algorithm                                                     |

| Figure 3.5. The effect of variety of number of virtual channels versus power             |

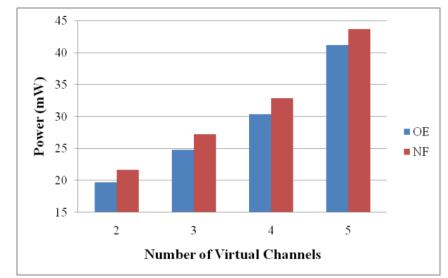

| consumption in OE and NF routing algorithm61                                             |

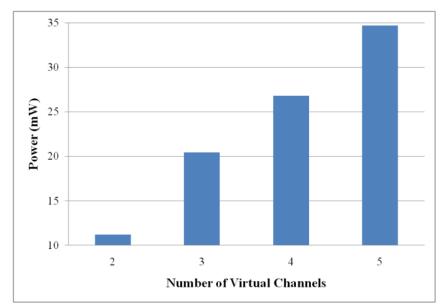

| Figure 3.6. The effect of variety of number of virtual channels versus power             |

| consumption in Duato routing algorithm                                                   |

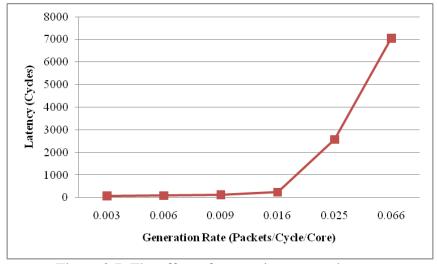

| Figure 3.7. The effect of generation rate on latency                                     |

| Figure 3.8. The effect of variety of number of virtual channels versus latency in X-Y    |

| routing algorithm                                                                        |

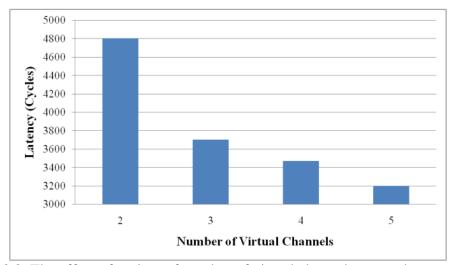

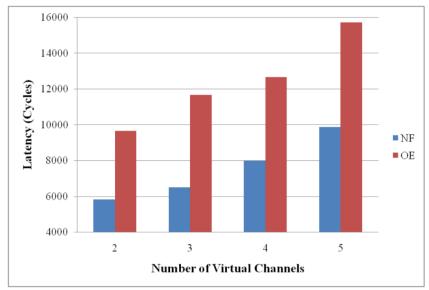

| Figure 3.9. The effect of variety of number of virtual channels versus latency in NF     |

| and OE routing algorithm                                                                 |

| Figure 3.10. The effect of variety of number of virtual channels versus latency in Duato |

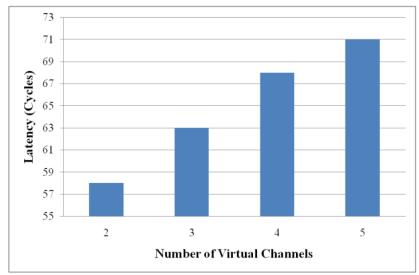

| routing algorithm                                                                        |

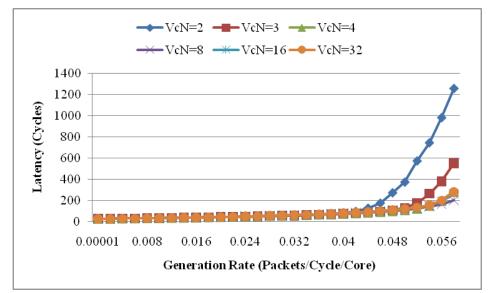

| Figure 3.11. The effect of generation rate and variety of number of virtual channels of virtual channels of the second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second second se | nels |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| versus latency in X-Y routing algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . 68 |

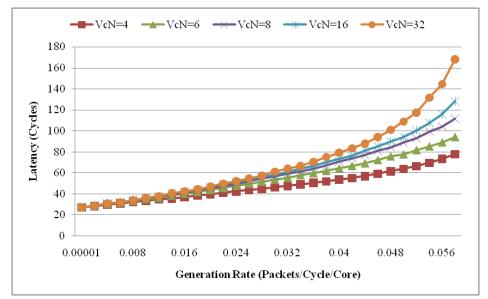

| Figure 3.12. The effect of generation rate and variety of number of virtual channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | iels |

| versus latency in Duato routing algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 68 |

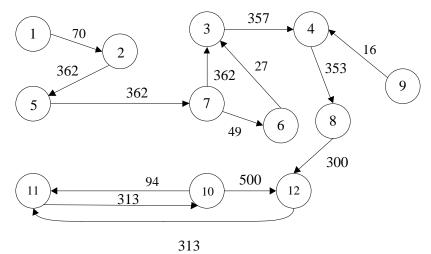

| Figure 3.13. Communication trace graph for VOPD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 80 |

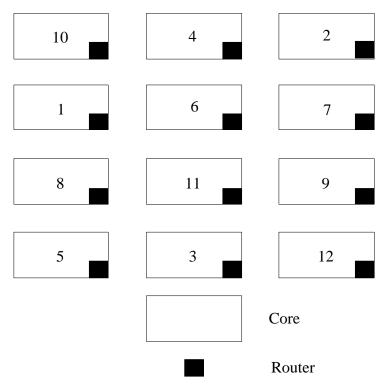

| Figure 3.14. Non-optimized layout for VOPD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 81 |

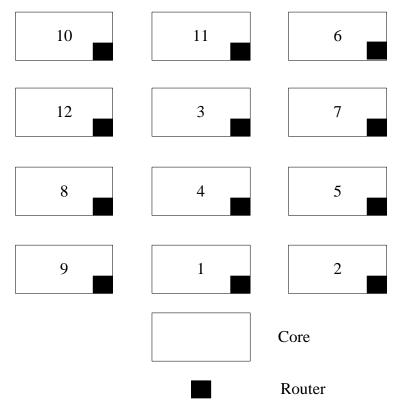

| Figure 3.15. Optimized layout for VOPD with proposed method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 82 |

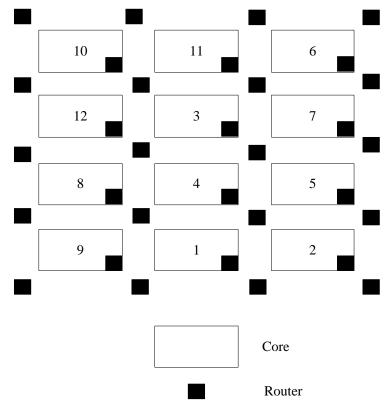

| Figure 3.16. Optimized VOPD layout with dummy and own routers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 83 |

| Figure 3.17. Optimized VOPD layout with optimum number of routers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 83 |

| Figure 3.18. Power comparison of non-optimized and QAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 84 |

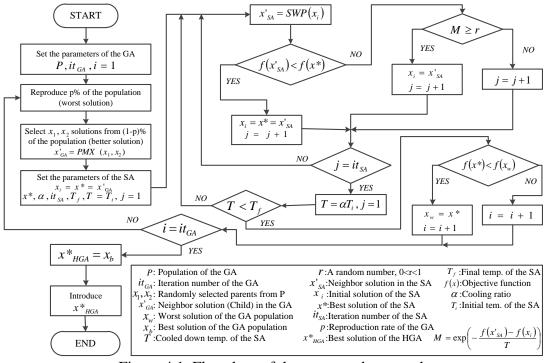

| Figure 4.1. Flowchart of the suggested approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 93 |

## LIST OF SYMBOLS/ABBREVIATIONS

| α                | Cooling ratio                                       |  |  |

|------------------|-----------------------------------------------------|--|--|

| Bavg             | Bit Average                                         |  |  |

| BI               | Bus Invert                                          |  |  |

| BMP              | Bitmap                                              |  |  |

| С                | Capacitance                                         |  |  |

| CABI             | Crosstalk Avoidance Bus Invert                      |  |  |

| CDBI             | Coupling Driven Bus Invert                          |  |  |

| Clk              | Clock Pulse                                         |  |  |

| СоМ              | Cost of Mapping                                     |  |  |

| CoR              | Cost of Router                                      |  |  |

| CTG              | Communication Task Graph                            |  |  |

| DOCX             | Microsoft Word Document in .docx format             |  |  |

| DPM              | Dynamic Power Management                            |  |  |

| DVS              | Dynamic Voltage Scaling                             |  |  |

| E(x)             | Expected Value                                      |  |  |

| GA               | Genetic Algorithm                                   |  |  |

| GIF              | Graphics Interchange Format                         |  |  |

| GR               | Generation Rate                                     |  |  |

| HTML             | Hyper Text Markup Language                          |  |  |

| it <sub>GA</sub> | Iteration of the Genetic Algorithm                  |  |  |

| ITRS             | International Technology Roadmap for Semiconductors |  |  |

| it <sub>sA</sub> | Iteration of the Simulated Annealing                |  |  |

| JPEG             | Joint Photographic Experts Group                    |  |  |

|                  | xvi                                                 |  |  |

| L     | Latency                                          |  |  |

|-------|--------------------------------------------------|--|--|

| LWC   | Limited Weight Coding                            |  |  |

| Mb    | Megabit                                          |  |  |

| MFLP  | Most Frequent Least Power                        |  |  |

| MILP  | Mixed Integer Linear Problem                     |  |  |

| MOCA  | Mesh based On Chip Interconnection Architectures |  |  |

| MPEG  | Moving Picture Experts Group                     |  |  |

| MWD   | Multi Window Display                             |  |  |

| NC    | No Coding                                        |  |  |

| NF    | North First                                      |  |  |

| NoC   | Network on Chip                                  |  |  |

| NP    | Nondeterministic Polynomial time                 |  |  |

| OE    | Odd Even                                         |  |  |

| OPAIC | Optimization technique for application specific  |  |  |

| Р     | Power Consumption                                |  |  |

| ŕ     | Population of the Genetic Algorithm              |  |  |

| PDF   | Portable Document Format                         |  |  |

| PNG   | Portable Network Graphics                        |  |  |

| QAP   | Quadratic Assignment Problem                     |  |  |

| S.A   | Switching Activity                               |  |  |

| SA    | Simulated Annealing                              |  |  |

| SoC   | System on Chip                                   |  |  |

| TD    | Time Duration                                    |  |  |

| $T_i$ | Initial Temperature of the Simulated Annealing   |  |  |

| TXT   | TeXT                                             |  |  |

VFI Voltage Frequency Island

VHDL VHSIC (Very High Speed Integrated Circuit) Hardware Description

Language

- VLSI Very Large Scale Integration

- VOPD Video Object Plane Decoder

- WAV Sound files in .wav format

- WSM Weighted Super Mesh

## Chapter 1

## **INTRODUCTION**

### **1.1 Introduction**

As technology shrinks, the integration of many Intellectual Property (IP) cores on a chip is increased. Thus, it is indispensible to manage the huge number of IP cores on a chip. Advances in Very Large Scale Integration (VLSI) technology have led researchers to create a system on a chip which is called System on Chip (SoC). The interconnection in SoCs has a colossal effect on the energy consumption and this contribution increases new families of VLSI [1]. However, SoC has some drawbacks, such as lack of scalability, reusability, unpredictable latency and high energy consumption [2]. Network on Chips (NoCs) have been proposed to alleviate today's communication problem of SoCs [2,3]. These advantages in NoC architecture came at the cost of complexity that has a colossal effect on power consumption and performance. Nowadays, power consumption has become a key issue in many core chip architecture. By shrinking the transistors in new VLSI families, the power consumed in cores and logics would not be dominant portion of power any more. Instead, the dominant portion is going toward the interconnection

#### **1.2 Network on Chip Architecture**

Nowadays, the integration of many cores on a single chip becomes technologically possible. VLSI design is moving toward of hundreds of processor and memory elements in System on Chip (SoC) architectures. Interconnection networks are utilized for various applications. Researchers have used an infrastructure to improve these interconnections by borrowing the concept of networking from computer network field which is called Network on Chip (NoC) [3]. Many challenges in SoC can be solved by NoC architecture [3]. Although these days some commercial products are using the NoC infrastructure to enjoy its privileges, there are still many challenges in this kind of network which have significant effect on SoCs [4].

The main advantages of NoC compared to the traditional bus based interconnections are as follows:

- NoCs avoid the crosstalk in ultra deep submicron technologies.

- NoCs has more scalability for segmentation of wires.

- NoCs are reliable, predictable and energy efficient.

- NoCs are performance efficient. Better deal with large bandwidth traffic.

- NoCs provide Globally Asynchronous Locally Synchronous (GALS) paradigm.

- NoCs use wire efficiently when using physical links among the IP cores.

- NoCs increase the degree of freedom in design due to the decentralization.

- NoCs are customizable. The customization allows designer to plan the NoCs to the specific applications.

- NoCs increase modularity. Hence, the procedure of the design is shortened.

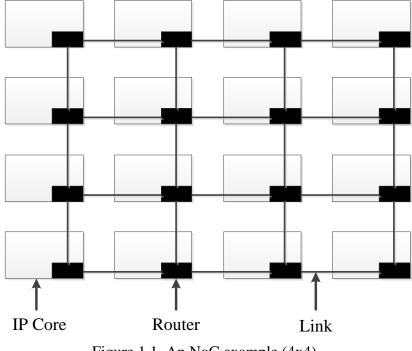

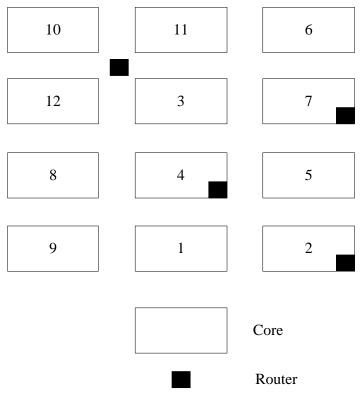

Figure 1.1 illustrates a 4x4 mesh NoC. As shown in the Figure, NoC is composed of links, routers and Network Interfaces (NIs). Links are used as a channel to connect the nodes. Routers route the data based on the routing protocol. The routers have some buffers as well. NIs provide connection between the IP cores and the NoC to organize transmission and reception of packets which is segmented into flow control units (flits). NIs are implemented into the IP cores or the routers.

Figure 1.1. An NoC example (4x4)

#### **1.3 Motivation**

Power consumption is one of the most important factors in NoC architectures. The power consumption of the NoC consists of power consumed by links and routers [5]. Some of the researchers worked in this area. As technology shrinks, due to the importance of the power reduction, there is a demanding need for improvement of power dissipation. In this dissertation, novel approaches are proposed to reduce the link power consumption and the power dissipation of routers along with the performance improvement.

The motivations behind this dissertation are as follows:

- To present a new low power encoding approach to shrink the power consumption in NoCs.

- Propose analytical methods to obtain the optimum layout for NoCs to reduce the energy dissipation.

- Suggest meta-heuristic approaches and fuzzy logic algorithms to improve the power consumption and the performance in NoCs.

#### **1.4 Thesis Overview**

The thesis consists of four chapters which is organized as follows:

Chapter one gives the introduction of the thesis. Chapter two presents a low power encoding approach for on chip networks. It starts with an introduction of power consumption of interconnections in SoCs and low power encoding. The chapter follows by the proposed low power encoding method and its optimality. The chapter then surveys the effectiveness of the presented algorithm. Eventually, the proposed method is evaluated with different characteristics of NoC.

Chapter three presents an optimization technique to improve energy consumption and performance in application specific NoCs. The motivation of using optimization technique in NoCs is discussed in details. The mathematical models are proposed in two main sections. The analytical proposed approaches in this chapter are examined by comparison with the previous work. Chapter four which is the conclusion and future work suggests fuzzy-based metaheuristic mapping algorithms for NoCs. It is suggested to utilize meta-heuristic, hybrid meta-heuristic algorithm and fuzzy logic to solve the QAP to obtain the optimum layout for NoCs. The bi-objective fuzzy-based hybrid meta-heuristic algorithm approaches are proposed through this chapter.

## Chapter 2

## LOW POWER ENCODING FOR ON CHIP NETWORKS

#### 2.1 Introduction

The technological trend in portable and battery-powered devices introduces the power as a new aspect of VLSI design [6,7]. The increased power consumption causes a lot of problems such as decreasing the life time, and increasing the cost of packaging [8]. A great deal of research is conducted to reduce the power consumption of interconnections in SoCs. Decreasing the swing voltage of power supply [9], using dual threshold voltage [10], voltage-frequency island (VFI) [11], activity postponement [12], Dynamic Voltage Scaling (DVS) [13], Dynamic Power Management (DPM) [14], statistical compression [15] and elimination of dispensable buffer slots [16] are some of the power reduction methods presented in the literature.

One of the solutions to decrease the power consumption in chip interconnections is low power encoding [17]. This method tries to decrease the number of switching activities and consequently the dynamic power. On the other hand, the power consumption of coder and decoder are the overhead of this method considered to evaluate its efficiency.

In this chapter, we propose a novel low power encoding approach to decrease the number of switching activities through decreasing the number of ones included in code words and sending the code words with transition signaling. Apparently, in transition signaling, the number of total switching activities is equal to the number of ones in the code words [18]. This thesis introduces a new algorithm to assign code words to symbols in such a way that the more frequent symbols consume less power. To approach this goal, the proposed Most Frequent Least Power (MFLP) encoding uses a tree-based infrastructure. The tree structure provides a set of symbols which assigns the fewer ones words to high probability data and vice versa. Based on the proposed algorithm the most frequent symbols are allocated to the least number of ones which results in the least power consumption.

Most of the low power encoding algorithms increase the width of the transmission bus to send the data [18-21], whereas the proposed method does not rely on spatial redundancy. It is also worth mentioning that even though in most of the traditional low power encoding algorithms the effect of coupling capacitors is ignored, our results show that these capacitors have an increasing contribution in power consumption in the NoCs as the VLSI technology advances and the size of the transistor shrinks. In this thesis, all evaluation results consider capacitors, coupling and self, to calculate the power consumption of links. The experimental results show that by applying the proposed approach, power dissipation up to 46% is improved and with, on an average, 14.4% area overhead.

#### **2.2 Literature Review**

Several methods have been proposed to reduce the power consumption by encoding techniques. These include the algorithms that have been designed for data line [19], irredundant encoding [22], correlated data, like address buses [23, 24], parallel and serial which are used for the parallel and serial buses, respectively [25], redundant

encoding method that raise either the number of transmission bus or clock pulses to send data [26], and adaptability [27-29].

One of the most well-known low power encoding is the Bus Invert coding [19]. This coding is appropriate for the uniform distribution data and the parallel bus which have spatial redundancy. Another scheme which tries to decrease the number of transitions is limited weight coding (LWC) [18]. In this algorithm, W is defined as a weight of each code word; that is, W is equal to the number of ones included in the code words. LWC applies transition signalling after assigning the code words and can be exploited in both the parallel that have spatial redundancy and serial buses with time redundancy. Beach coding [21] is suggested when the correlation of data pattern is computable. In this approach, the method of encoding is selected based on the pattern of data; therefore, it is strongly application dependent.

Since the power of links in NoCs is an important portion of power consumption, low power encoding also is applicable for this infrastructure. Researchers in [22] present an irredundant encoding and in [17, 30] a set of data encoding methods are proposed to decrease the link power consumption in the NoCs. This is worth mentioning that redundant encoding algorithm cannot decrease the power consumption in NoCs because this redundancy may cause redundancy in each router which is not compensated by power reduction in links. Moreover, due to the fact that in the advanced technology the links are too close to each other the low power encoding used in the NoCs should consider the transition on coupling capacitance as well.

#### **2.3 Proposed Method**

The main idea of the proposed method is to reduce the number of ones in code words. In fact, due to the transition signaling, the number of total switching activities is equal to the number of ones in code words [18]. The proposed method is a treebased algorithm. This tree encompasses root, a number of nodes and leaves. In this tree, code words are represented according to the location of the nodes referring to the data words.

#### 2.3.1 MFLP Encoding Approach

Our approach uses the tree-based structure to assign the code word with less ones to most frequent words; hence, we called it Most Frequent Least Power (MFLP) consumption coding. The objective is to minimize expectation of '1' and in turn, decrease the switching activities as well as the power consumption by using transition signaling. The tree-based structure also allows us to assign the shortest code words to more frequent symbols. Hence, this coding algorithm not only decreases the power consumption but also compresses the amount of transmitted data. Required statistical knowledge about frequencies of symbols are collected in previous time sliding windows; in other word, while data is passing, the frequency of data can be counted and this knowledge can be used to encode the data for next time sliding windows; evidently, the current data is being coded based on the statistical information gathered in previous time sliding window. MFLP coding is collecting this information while data is passing and because the sliding windows is small enough, the characteristic of data is likely be same in consecutive period of data. At first, we need to choose a parameter called division factor. According to this factor, we divide the words into two parts. This factor indicates that we are going either decrease the power or compress data. The tree is made of nodes, where each node has a label indicating the sum of labels of its children. In the case of leaf, this label refers to the frequency of words represented by this node. This tree structure can be created reversely; after dividing the words of data in two portions according to division factor, we assign the sum of these nodes as a label of the root. The root's label represents the sum of label of its children. We continue the procedure until the leaf of the tree which refers to each word of the data. This function is implemented in hardware and inserted in coder and decoder. The pseudocode of the proposed algorithm is presented in Figure 2.1.

```

Given sorted frequencies of symbols as

\{A_i \mid 1 \leq i \leq n \mid \forall i, j, A_i < A_j \rightarrow f_i < f_j // \text{ symbol } A_i \text{ has frequency} \}

fi

; chosen division factor = \gamma

function MFLP-tree (S = \{(A_i, f_i), ..., (A_k, f_k)\}) // j and k are

first and last index of symbols, respectively

T_1 \leftarrow \sum_{i=1}^n f_i // root of tree whose label is sum of all

frequencies in S

if (j = i)

insert a node labeled T_1

else

{

divide S into two subsets, S_1 = \{(A_j, f_j), \dots, (A_{\lceil \gamma k \rceil}, f_{\lceil \gamma k \rceil})\}, S_2 =

\{(A_{|\gamma k+1|}, f_{|\gamma k+1|}), \dots, (A_k, f_k)\} // two sub sets are generated to

create children of root

MFLP-tree (S_1); // function is called recursively for

children named S_1 and S_2

MFLP-tree (S_2) }

end

```

Figure 2.1. Pseudocode of the proposed algorithm

In this algorithm,  $A_i$  is the word of the data whose frequency is  $f_i$  and S is a set of data words.  $T_i$  is the MFLP tree node labeled by the sum of its children's frequency.

With reference to Figure 1, the tree construction can be further explained with the following steps:

- We sort the frequencies of symbols in descending order from higher frequencies to lower ones.

- We choose division factor ( $\gamma$ ) according to the goal, either to decrease the power consumption or to compress the amount of data.

- MFLP function constructs the tree reversely. We have to provide the frequency of data words as input of this function. It divides the data words based on *γ* in two portions as upper and lower groups. Sum of the upper and lower group frequencies is allocated to the left and right nodes, respectively. After that, it invokes itself reversely to construct interior nodes. This algorithm continues till the leaf nodes are generated.

- The labels "0" and "1" are assigned to the edge of upper and lower group, respectively.

- To figure out the code words, we follow the labels of the edges. The code word is the sequence of the edge labels from root to the frequencies of the symbol.

The procedure of encoding in MFLP is composed of two steps: Counting and Coding. While data is passing from encoder the frequency of transmitted symbols can be counted in a time sliding window; this knowledge let encoder generate the tree structure and assign new code words to the symbols. These new codes are going to be used in the next sliding window. It is clear that meanwhile data is coded based on knowledge of previous window (coding), the frequencies of symbols in current window can be counted to be used in the next window (counting). It is obvious that these two steps can take place at the same time. According to the proposed algorithm, data stream should be divided into the sections with same time period namely sliding window. The frequency of data is counted in current window and will be used in the next sliding window to provide the final code words. Due to temporal locality, the frequencies generated in the previous window can be used in the current window. The same procedure is applied to the decoder to figure out the frequency of received data before decoding.

In the following example, we clarify the steps of the algorithm.

- First step: the symbols should be arranged according to their frequency of occurrence in descending order. For instance, there are 13 symbols which are given to be coded. At first we organize them in alphabetical order: A,B,C,D,E,F,G,H,N,P,Q,R,S.

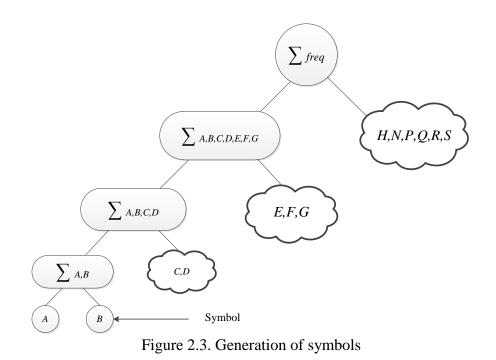

- Second step: This step depends on the division factor. This value should be multiplied by the number of symbols. The selection of the symbols is based on the result of the last multiplication. Top symbols should be located on the left and the others on the right. This strategy is shown in Figure 2.2.

Figure 2.2. Root and its children

It is required to repeat the second step for the symbols which are included in the left hand side. Figure 2.3 shows the steps to reach to the symbols. This trend must be continued for each node either in the left hand side or in the right hand side till we get to one symbol in every set.

- Third step: in this step, we assign 0 and 1 to the left and right hand side of the leaves respectively.

- Forth step: in this last step, traversing from the root to the leaves of the tree the code word is found. The result of this example is shown in Table 2.1.

| Table 2.1. The code word with different coding |           |      |         |       |

|------------------------------------------------|-----------|------|---------|-------|

| Symbol                                         | Frequency | MFLP | Huffman | 3-LWC |

| А                                              | 20        | 0000 | 10      | 0111  |

| В                                              | 18        | 0001 | 000     | 1110  |

| С                                              | 4         | 1000 | 00101   | 0110  |

| D                                              | 4         | 1001 | 00110   | 1000  |

| E                                              | 3         | 1101 | 001110  | 0001  |

| F                                              | 1         | 111  | 001111  | 0000  |

| G                                              | 4         | 101  | 01000   | 0100  |

| Н                                              | 4         | 1100 | 01001   | 0010  |

| Ν                                              | 6         | 0101 | 0101    | 0011  |

| Р                                              | 10        | 0010 | 011     | 0101  |

| Q                                              | 6         | 011  | 00100   | 1100  |

| R                                              | 10        | 0011 | 110     | 1010  |

| S                                              | 10        | 0100 | 111     | 1001  |

In Table 1, the code word generated with MFLP is also compared with the Huffman tree and 3-LWC. We calculate the expectation of ones for symbols by Eq. 2.1.

$$E(x) = \sum_{i=0}^{symbol} F_i * N_i$$

(2.1)

where  $F_i$  is the frequency of the symbols and  $N_i$  is the number of ones for each symbol in the tree.

The tree structure assigns a code word with fewer ones to the more frequent data words. According to Eq. 1, the expectation of ones can be minimized by this strategy. When time duration remains constant, decreasing the power consumption can lead to decrease the energy dissipation. In the case of compression, the energy can be reduced due to decrease in the duration of time provided that either switching activity does not rise or its increment can be compensated by time reduction. Hence, there is a trade-off between the number of switching activities and compression ratio which depends on the division factor. The effect of division factor on compression and power consumption can be evaluated on these bases:

- 1- As the division factor is increased, we assign the symbols with fewer ones to more frequent data words resulting in less switching activities thereby reducing the power consumption.

- 2- By reducing the division factor, we can improve the compression ratio. Tree structure allocates small length symbols to more frequent data words at the expense of increasing the number of ones and consequently power dissipation.

To examine how the proposed method reduces the number of switching activities and power consumption, we evaluate the bit average by Eq. 2.2.

$$B_{avg} = \sum_{i=0}^{symbol} F_i * L_i \tag{2.2}$$

where  $F_i$  is the frequency of symbol whose length is  $L_i$ .

### 2.3.2 Optimality of MFLP

In this subsection, we present the mathematical proof to show that MFLP, which aims to reduce the power consumption by decreasing the number of ones in the code word, is able to reduce the expectation of ones. Therefore, the MFLP code is optimal if the expected value of ones is minimal. The frequency of symbols are ordered, so that  $F_1 \ge F_2 \ge \cdots \ge F_i$ . To prove that the E(x) in MFLP code is minimal, we show that with any changes in MFLP's tree and code word the value of expected value is increased. We consider that  $C_w$  is an optimal code word which is the result of MFLP encoding. If  $F_j \ge F_k$  then  $N_k \ge N_j$ . We then swap MFLP code words. Supposing that  $C'_w$  is the code words j and k of  $C_w$  interchanged, the expected value of  $C'_w$  is shown in Eq. 2.3.

$$E(C'_{w}) = \sum_{i=0}^{symbol} F_{i} * N'_{i}$$

(2.3)

$N'_i$  is the number of ones for symbol after interchanging  $j^{th}$  and  $k^{th}$  code words.

$$E(C'_{w}) = \sum_{i=0}^{symbol} F_{i} * N'_{i} = F_{j} * N_{k} + F_{k} * N_{j}$$

$$E(C'_{w}) - E(C_{w}) = \sum_{i=0}^{symbol} F_{i} * N'_{i} - \sum_{i=0}^{symbol} F_{i} * N_{i}$$

$$= (F_{j} * N_{k} + F_{k} * N_{j}) - (F_{j} * N_{j} + F_{k} * N_{k})$$

$$= (F_{j} - F_{k})(N_{k} - N_{j})$$

Based on MFLP, if  $F_j \ge F_k$  then  $N_k \ge N_j$ , which means that  $E(C'_w) - E(C_w)$ should be greater than zero  $(E(C'_w) \ge E(C_w))$ . It can be concluded that after changing the code word of MFLP, the value of expected value is increased. Hence, the minimum amount of expected value, the minimum number of ones, is related to MFLP code words and  $C_w$  is optimal.

#### 2.4 Effective Criteria in the Efficiency of the Proposed Method

By adding coding algorithm to the system, the power consumption of coder and decoder are considered as overhead and is needed to be compensated. The power consumptions of transmission line without (2.5) and with (2.6) using encoding algorithm are calculated by:

$$P_{link} = P_{self} + P_{coupling} \tag{2.4}$$

$$P_{link} = \propto_s C_{self} V_{dd}^2 f + \propto_c C_{coupling} V_{dd}^2 f$$

(2.5)

$$P_{after} = P_{cod} + P_{dec} + \alpha_{as} C_{self} V_{dd}^2 f + \alpha_{ac} C_{coupling} V_{dd}^2 f$$

(2.6)

$$C_{link} = C_{self} + C_{coupling} \tag{2.7}$$

$P_{link}$  is power dissipation before using encoding algorithm and  $P_{after}$  is the power after inserting MFLP.  $P_{link}$  is composed of power of self capacitance ( $P_{self}$ ) and coupling capacitance ( $P_{coupling}$ ). As shown in (2.5),  $\propto_s$  and  $\propto_c$  are switching activity of the self and coupling capacitances, respectively.

$P_{after}$  is power consumption after using encoding approach.  $P_{cod}$  and  $P_{dec}$  are the power dissipation of coder and decoder, respectively, $\propto_{as}$  and  $\propto_{ac}$  are switching activity on self and coupling capacitances after applying data coding approach.

$C_{link}$  is the total capacitance which is the summation of the self ( $C_{self}$ ) and coupling ( $C_{coupling}$ ) capacitance, f is the clock frequency and  $V_{dd}$  is the power supply of the system.

$\propto_s$  and  $\propto_{as}$  which are the self-switching activity before and after using encoding method are evaluated based on the number of transition ( high to low and vice versa) on the link. The coupling switching activity before and after using MFLP ( $\propto_c$ and  $\propto_{ac}$ ) are calculated according to the direction of switching activities happening on the consecutive wires which is shown in Table 2.2.

The evaluation of self and coupling capacitance is based on the type of the switching activity. In Table 2.2 the number of self and coupling transition for different type of switching activities are depicted.

The coding algorithm can decrease the power consumption, provided that  $P_{after}$  is less than the power consumed before applying MFLP. The more the number of switching activities decreased, the more effective our method is. Efficiency factor ( $\beta$ ) is introduced in order to evaluate MFLP.

$$P_{after} = P_{codec} + \alpha_{as} C_{self} V_{dd}^2 f + \alpha_{ac} C_{coupling} V_{dd}^2 f$$

(2.8)

where  $P_{codec}$  is sum of the power consumption of coder and decoder. As a result, the efficiency factor can be expressed as

$$\beta = \frac{(\alpha_s - \alpha_{as})C_{self}V_{dd}^2 f + (\alpha_c - \alpha_{ac})C_{coupling}V_{dd}^2 f}{P_{codec}}$$

(2.9)

MFLP can reduce the power dissipation if the value of efficiency factor ( $\beta$ ) is more than one.

| Туре                                                    | Number of<br>Self<br>Transition | Number of<br>Coupling<br>Transition |

|---------------------------------------------------------|---------------------------------|-------------------------------------|

|                                                         | 1                               | 1                                   |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$ | 0                               | 0                                   |

|                                                         | 2                               | 0                                   |

|                                                         | 2                               | 4                                   |

Table 2.2. Number of Self and Coupling capacitances for different type of switching activities

Assessment of some of the parameters' effectiveness of our approach is presented below:

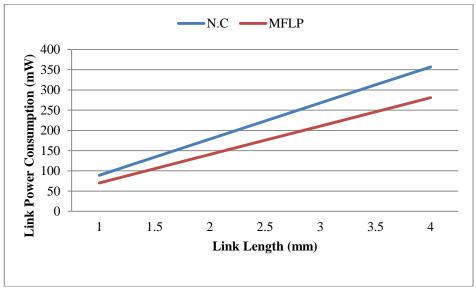

*Distance*: One of the most important criterion that affects the efficiency factor is the distance between the transmitter and receiver nodes. Distance has an important role on the amount of capacitance of the link and consequently on the power consumption of the NoC when the switching activity occurs. In other words, by increasing the distance between the transmitter and receiver, the value of the capacitance of links

increases. This shows that reduction of the number of transitions on the link plays a more effective role in the improvement of power consumption of the NoC. It is evident that according to Eq. 2.9, the value of the efficiency factor ( $\beta$ ) increases due to the increased value of C. Thus, our approach is more effective in longer distances. *Family*: With the growth of advanced VLSI technology, the transistors shrink and the length of the wire remains constant or even increases. Eventually, the capacitance of the wire gets more dominant. Therefore, based on Eq. 2.9, the efficiency factor increases and consequently MFLP becomes much more effective.

## 2.5 Evaluation

The power of the NoC is consumed in two parts, the routers and the links. It should be mentioned that the power of Network Interface (NI) is included in the power of router. In our experiment, the baseline network contains 16 nodes which are connected in a mesh topology whose router algorithm is XY; each router has 2 virtual channels. Packet length is 32 flits. We use power compiler tool from Synopsys<sup>1</sup> to calculate the power of the routers. Power compiler considers the static and dynamic power consumptions. The number of transitions is the major factor indicating dynamic power consumption in data transmission. Despite the fact that the growth of VLSI technology and shrinking the transistor size make the static power dominant part of the power consumption, the research has shown that in the NoC infrastructure the dynamic power still remains the prevalent portion of the power consumption due to its architecture.

<sup>&</sup>lt;sup>1</sup> Synopsys is registered trademarks

The power of the links is determined by Eq. 2.4. We used 65nm technology for the simulations of the proposed method. According to the International Technology Roadmap for Semiconductors [1], for this technology  $V_{dd}$  is defined as 1 Volt and the clock frequency is set to 500 MHz based on the critical path of the system. The length of the metal wires is selected as 2 mm for the mesh topology. The self capacitance of the wire links and coupling capacitance are selected as 0.2 pF/mm and 0.6 pF/mm, respectively. The transitions of wires are calculated by Modelsim<sup>2</sup>.

In this section, the coder and decoder are inserted in the local link, between the routers and process elements. In other words, this service is delivered in the transport layer of the NoC which is offered in transmitter and receiver. Hence, the data encoding is done end to end. The coding methods and the NoC infrastructure are implemented in VHDL.

## 2.5.1 Evaluation of the Proposed Algorithm

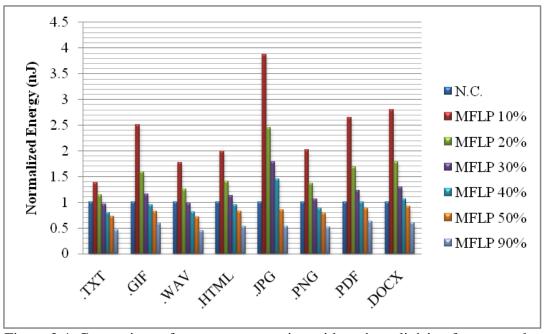

It does not matter which infrastructure the designers have chosen, either the traditional bus or the novel NoCs, this coding can be useful for all. To show the effectiveness of our algorithm, we examine its effect in decreasing the power consumption or the amount of data by using some real-life streams. We assess MFLP in the following cases: using buses as a traditional infrastructure and the NoC as a new one.

#### 2.5.1.1 On the Bus

To evaluate our approach we consider a system including a transmitter, a communication bus and a receiver. The power can be calculated in two cases:

<sup>&</sup>lt;sup>2</sup> Modelsim is registered trademarks

original data and coded version. The power of the link consists of power consumed in the coupling and self capacitances.

On the serial bus, length of the metal wires is assumed as 2 mm and the self capacitance of the wire links is selected as 0.2 pF/mm [1]. It is worth mentioning that on the serial bus we do not have any significant coupling capacitance. The designer needs to decide whether power reduction or decreasing the amount of data is the final goal. According to this decision we need to change the division factor. The more we increase the division factor, the more the bit average goes up. That is, we have gained more power reduction in expense of increasing the amount of data. We evaluate our approach in various division factors for the serial bus using MFLP encoding and the results are shown in Table 2.3 and Figure 2.4.

In the serial system, the energy is calculated by multiplying the power consumption and time duration. It is apparent that the time duration can be estimated by:

$$T = B_{ave} * S * Clk \tag{2.10}$$

Where *T* is time duration,  $B_{avg}$  is bit average, S indicates the number of transmitted symbols, and *Clk* is the period of clock in the transmission system. Consequently, the bit average is able to represent the time duration because other parameters are constant with different division factors.

The energy dissipation before applying encoding algorithm and after using MFLP are evaluated based on the following formula:

$$E_{B.C.} = E_{Router} + E_{Link} \tag{2.11}$$

$$E_{A.C.} = E_{Router} + E_{Codec} + E_{CLink}$$

(2.12)